## Precision Dual/Quad CMOS Rail-to-Rail Input/ Output Amplifiers

#### **FEATURES**

■ Maximum Offset Voltage: 70µV (25°C)

Maximum Offset Drift: 0.8µV/°C

■ Maximum Input Bias: 1pA (25°C) 40pA ( $T_A \le 85$ °C)

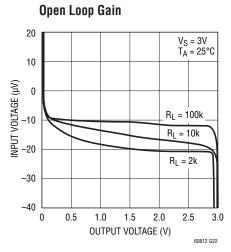

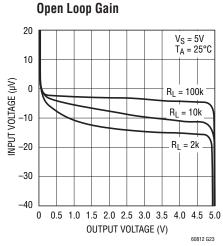

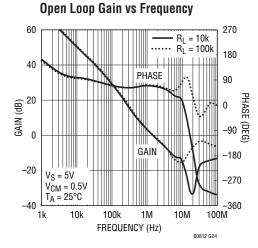

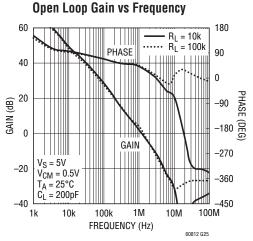

Open Loop Voltage Gain: 120dB TypGain Bandwidth Product: 3.6MHz

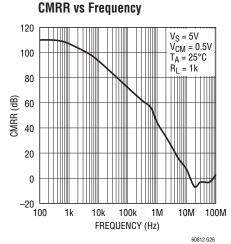

CMRR: 100dB MinPSRR: 98dB Min

0.1Hz to 10Hz Noise: 1.3µV<sub>P-P</sub>

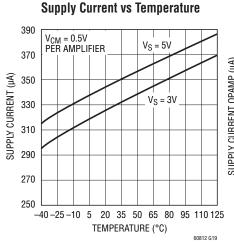

Supply Current: 330µA

Rail-to-Rail Inputs and Outputs

Unity Gain Stable

2.7V to 5.5V Operation Voltage

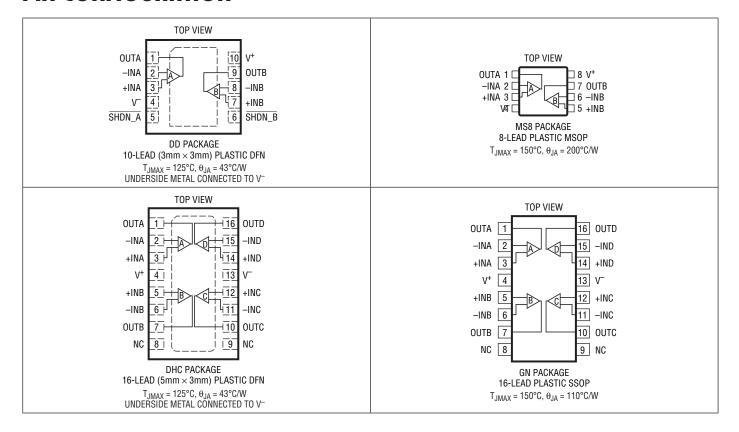

Dual LTC6081 in 8-Lead MSOP and 10-Lead DFN10 Packages; Quad LTC6082 in 16-Lead SSOP and DFN Packages

#### **APPLICATIONS**

- Photodiode Amplifier

- Strain Gauge

- High Impedance Sensor Amplifier

- Microvolt Accuracy Threshold Detection

- Instrumentation Amplifiers

- Thermocouple Amplifiers

## DESCRIPTION

The LTC®6081/LTC6082 are dual/quad low offset, low drift, low noise CMOS operational amplifiers with rail-to-rail input/output swing.

The  $70\mu V$  maximum offset, 1pA input bias current, 120dB open loop gain and  $1.3\mu V_{P-P}$  0.1Hz to 10Hz noise make it perfect for precision signal conditioning. The LTC6081/LTC6082 features 100dB CMRR and 98dB PSRR.

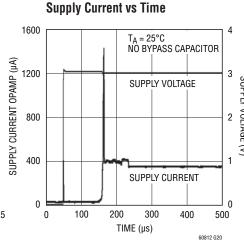

Each amplifier consumes only  $330\mu A$  of current on a 3V supply. The 10-lead DFN has an independent shutdown function that reduces each amplifier's supply current to  $1\mu A$ .

LTC6081/LTC6082 is specified for power supply voltages of 3V and 5V from -40°C to 125°C. The dual LTC6081 is available in 8-lead MSOP and 10-lead DFN10 packages. The quad LTC6082 is available in 16-lead SSOP and DFN packages.

$\mathcal{L}$ 7, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

## TYPICAL APPLICATION

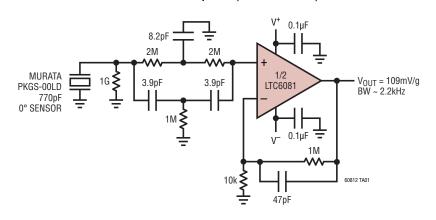

#### **Shock Sensor Amplifier (Accelerometer)**

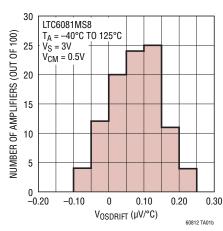

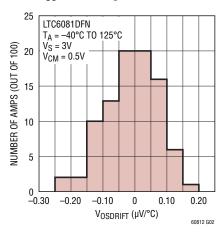

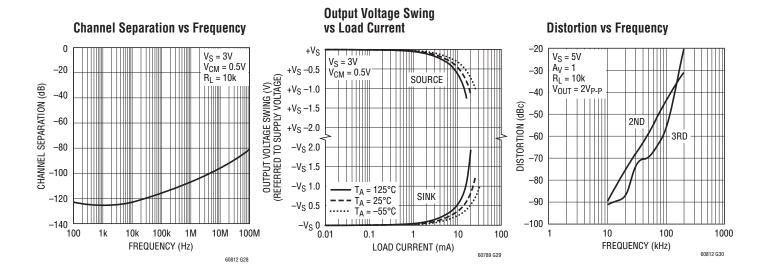

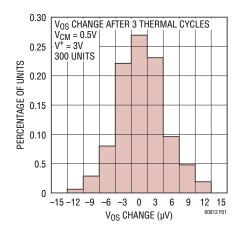

#### Vos Drift Histogram

## **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> ) | 6V              |

|----------------------------------------------------------|-----------------|

| Input Voltage                                            |                 |

| Output Short Circuit Duration (Note 2)                   | Indefinite      |

| Operating Temperature Range (Note 3)                     |                 |

| LTC6081C, LTC6082C                                       | –40°C to 85°C   |

| LTC6081I, LTC6082I                                       | –40°C to 85°C   |

| LTC6081H, LTC6082H                                       | –40°C to 125°C  |

| (H Temperature Range Not Available                       | in DFN Package) |

|                                                          |                 |

| Specified Temperature Range (Note 4)  |                |

|---------------------------------------|----------------|

| LTC6081C, LTC6082C                    | 0°C to 70°C    |

| LTC6081I, LTC6082I                    | –40°C to 85°C  |

| LTC6081H, LTC6082H                    | 40°C to 125°C  |

| Junction Temperature                  |                |

| DFN Packages                          | 125°C          |

| All Other Packages                    | 150°C          |

| Storage Temperature Range             |                |

| DFN Packages                          | –65°C to 125°C |

| All Other Packages                    | –65°C to 150°C |

| Lead Temperature (Soldering, 10 Sec). | 300°C          |

## PIN CONFIGURATION

## **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | SPECIFIED TEMPERATURE RANGE |

|------------------|-------------------|---------------|---------------------------------|-----------------------------|

| LTC6081CDD#PBF   | LTC6081CDD#TRPBF  | LCJP          | 10-Lead (3mm × 3mm) Plastic DFN | 0°C to 70°C                 |

| LTC6081IDD#PBF   | LTC6081IDD#TRPBF  | LCJP          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C               |

| LTC6081CMS8#PBF  | LTC6081CMS8#TRPBF | LTCJN         | 8-Lead Plastic MSOP             | 0°C to 70°C                 |

| LTC6081IMS8#PBF  | LTC6081IMS8#TRPBF | LTCJN         | 8-Lead Plastic MSOP             | -40°C to 85°C               |

| LTC6081HMS8#PBF  | LTC6081HMS8#TRPBF | LTCJN         | 8-Lead Plastic MSOP             | -40°C to 125°C              |

| LTC6082CDHC#PBF  | LTC6082CDHC#TRPBF | 6082          | 16-Lead (5mm × 3mm) Plastic DFN | 0°C to 70°C                 |

| LTC6082IDHC#PBF  | LTC6082IDHC#TRPBF | 6082          | 16-Lead (5mm × 3mm) Plastic DFN | -40°C to 85°C               |

| LTC6082CGN#PBF   | LTC6082CGN#TRPBF  | 6082          | 16-Lead Plastic SSOP            | 0°C to 70°C                 |

| LTC6082IGN#PBF   | LTC6082IGN#TRPBF  | 60821         | 16-Lead Plastic SSOP            | -40°C to 85°C               |

| LTC6082HGN#PBF   | LTC6082HGN#TRPBF  | 6082H         | 16-Lead Plastic SSOP            | -40°C to 125°C              |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . Test conditions are $V^+ = 3V$ , $V^- = 0V$ , $V_{CM} = 0.5V$ unless otherwise noted.

|                          |                                                                         |                                                                                                                          |   |                          |                          |                      | H SUFFIX             |                          |                |                             |

|--------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---|--------------------------|--------------------------|----------------------|----------------------|--------------------------|----------------|-----------------------------|

| SYMBOL                   | PARAMETER                                                               | CONDITIONS                                                                                                               |   | MIN                      | SUFFI)<br>TYP            | MAX                  | MIN                  | TYP                      | MAX            | UNITS                       |

| V <sub>0S</sub>          | Offset Voltage                                                          | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                    | • | -70<br>-90<br>-70<br>-90 |                          | 70<br>90<br>70<br>90 | -70<br>-90           |                          | 70<br>90       | μV<br>μV<br>μV              |

| $\Delta V_{OS}/\Delta T$ | Input Offset Voltage Drift<br>(Note 5)                                  |                                                                                                                          | • |                          | ±0.2                     | ±0.8                 |                      | ±0.2                     | ±0.8           | μV/°C                       |

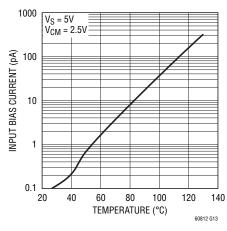

| I <sub>B</sub>           | Input Bias Current<br>(Note 6)                                          |                                                                                                                          | • |                          | 0.2                      | 1<br>40              |                      | 0.2                      | 1<br>500       | pA<br>pA                    |

| I <sub>OS</sub>          | Input Offset Current                                                    |                                                                                                                          | • |                          | 0.1                      | 15                   |                      | 0.1                      | 100            | pA<br>pA                    |

| e <sub>n</sub>           | Input Referred Noise                                                    | Noise Density at f = 1kHz<br>Integrated Noise From 0.1Hz to 10Hz                                                         |   |                          | 13<br>1.3                |                      |                      | 13<br>1.3                |                | nV/√Hz<br>μV <sub>P-P</sub> |

| In                       | Input Noise Current Density (Note 7)                                    |                                                                                                                          |   |                          | 0.5                      |                      |                      | 0.5                      |                | fA/√Hz                      |

|                          | Input Common Mode Range                                                 |                                                                                                                          | • | V-                       |                          | V <sup>+</sup>       | V-                   |                          | V <sup>+</sup> | V                           |

| C <sub>DIFF</sub>        | Differential Input Capacitance                                          |                                                                                                                          |   |                          | 3                        |                      |                      | 3                        |                | pF                          |

| C <sub>CM</sub>          | Common Mode Input<br>Capacitance                                        |                                                                                                                          |   |                          | 7                        |                      |                      | 7                        |                | pF                          |

| CMRR                     | Common Mode Rejection<br>Ratio                                          | V <sub>CM</sub> = 0V to 1.5V<br>V <sub>CM</sub> = 0V to 1.5V<br>V <sub>CM</sub> = 0V to 3V<br>V <sub>CM</sub> = 0V to 3V | • | 95<br>88<br>93<br>88     | 105<br>100<br>105<br>100 |                      | 95<br>86<br>93<br>86 | 105<br>100<br>105<br>100 |                | dB<br>dB<br>dB<br>dB        |

| PSRR                     | Power Supply Rejection Ratio                                            | V <sub>S</sub> = 2.7V to 5.5V                                                                                            | • | 98<br>96                 | 110                      |                      | 98<br>96             | 110                      |                | dB<br>dB                    |

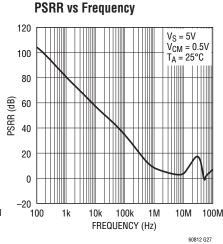

| V <sub>OUT</sub>         | Output Voltage, High, Either<br>Output Pin                              | No Load<br>I <sub>SOURCE</sub> = 0.5mA<br>I <sub>SOURCE</sub> = 5mA                                                      | • | -32<br>-320              | 1                        |                      | -35<br>-350          | 1                        |                | mV<br>mV<br>mV              |

|                          | Output Voltage, Low, Either<br>Output Pin (Referred to V <sup>-</sup> ) | No Load<br>I <sub>SINK</sub> = 0.5mA<br>I <sub>SINK</sub> = 5mA                                                          | • |                          | 1                        | 33<br>300            |                      | 1                        | 40<br>360      | mV<br>mV<br>mV              |

| A <sub>VOL</sub>         | Large-Signal Voltage Gain                                               | $R_{LOAD} = 10k, 0.5V < V_{OUT} < 2.5V$                                                                                  | • | 110                      | 120                      |                      | 110                  | 120                      |                | dB                          |

| I <sub>SC</sub>          | Output Short-Circuit Current                                            | Source<br>Sink                                                                                                           | • | 17<br>17                 |                          |                      | 15<br>15             |                          |                | mA<br>mA                    |

| SR                       | Slew Rate                                                               | A <sub>V</sub> = 1                                                                                                       |   |                          | 1                        |                      |                      | 1                        |                | V/µs                        |

| GBW                      | Gain-Bandwidth Product<br>(f <sub>TEST</sub> = 50kHz)                   | R <sub>L</sub> = 100k                                                                                                    | • | 2.5<br>1.8               | 3.6                      |                      | 2.5<br>1.5           | 3.6                      |                | MHz<br>MHz                  |

| Φ0                       | Phase Margin                                                            | R <sub>L</sub> = 10k                                                                                                     |   |                          | 70                       | -                    |                      | 70                       |                | Deg                         |

| ts                       | Settling Time 0.1%                                                      | A <sub>V</sub> = 1, 1V Step                                                                                              |   |                          | 6                        |                      |                      | 6                        |                | μs                          |

| l <sub>S</sub>           | Supply Current<br>(Per Amplifier)                                       | No Load                                                                                                                  | • |                          | 330                      | 400<br>435           |                      | 330                      | 400<br>460     | μA<br>μA                    |

|                          | Shutdown Current<br>(Per Amplifier)                                     | Shutdown, $V_{\overline{SHDN}} \le 0.8V$                                                                                 | • |                          | 0.5                      | 2                    |                      |                          |                | μA<br>μA                    |

| Vs                       | Supply Voltage Range                                                    | Guaranteed by the PSRR Test                                                                                              | • | 2.7                      |                          | 5.5                  | 2.7                  |                          | 5.5            | V                           |

|                          | Channel Separation                                                      | $f_S = 10kHz, R_L = 10k$                                                                                                 |   |                          | -120                     |                      |                      | -120                     |                | dB                          |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}C$ . Test conditions are $V^+ = 3V$ , $V^- = 0V$ , $V_{CM} = 0.5V$ unless otherwise noted.

|                  |                           |                                                      |   |     | I SUFFIX | (ES | ŀ   | SUFFIX | (   |       |

|------------------|---------------------------|------------------------------------------------------|---|-----|----------|-----|-----|--------|-----|-------|

| SYMBOL           | PARAMETER                 | CONDITIONS                                           |   | MIN | TYP      | MAX | MIN | TYP    | MAX | UNITS |

|                  | Shutdown Logic            | SHDN High<br>SHDN Low                                | • | 2   |          | 0.8 | 2   |        | 0.8 | V     |

| THD              | Total Harmonic Distortion | $f = 10kHz, V^+ = 3V, V_{OUT} = 1V_{P-P}, R_L = 10k$ |   |     | -90      |     |     | -90    |     | dB    |

| t <sub>ON</sub>  | Turn-On Time              | $V_{\overline{SHDN}} = 0.8V \text{ to } 2V$          |   |     | 10       |     |     | 10     |     | μs    |

| t <sub>OFF</sub> | Turn-Off Time             | V <sub>SHDN</sub> = 2V to 0.8V                       |   |     | 2        |     |     | 2      |     | μs    |

|                  | SHDN Pin Current          | V <sub>SHDN</sub> = 0V                               | • |     |          | 2   |     |        |     | μА    |

# The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . Test conditions are $V^+ = 5V$ , $V^- = 0V$ , $V_{CM} = 0.5V$ unless otherwise noted.

|                          |                                                                          |                                                                                            |            |   | <b>C</b> , I             | SUFFIX           | ŒS                   | I               | H SUFFI          | X              |                             |

|--------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------|---|--------------------------|------------------|----------------------|-----------------|------------------|----------------|-----------------------------|

| SYMBOL                   | PARAMETER                                                                | CONDITIONS                                                                                 |            | Ī | MIN                      | TYP              | MAX                  | MIN             | TYP              | MAX            | UNITS                       |

| V <sub>OS</sub>          | Offset Voltage                                                           | LTC6081MS8, LTC6082GN                                                                      | .5V<br>.5V | • | -70<br>-90<br>-70<br>-90 |                  | 70<br>90<br>70<br>90 | -70<br>-90      |                  | 70<br>90       | μV<br>μV<br>μV              |

| $\Delta V_{0S}/\Delta T$ | Input Offset Voltage Drift<br>(Note 8)                                   |                                                                                            |            | • |                          | ±0.2             | ±0.8                 |                 | ±0.2             | ±0.8           | μV/°C                       |

| I <sub>B</sub>           | Input Bias Current                                                       |                                                                                            |            | • |                          | 0.2              | 40                   |                 | 0.2              | 500            | pA<br>pA                    |

| I <sub>OS</sub>          | Input Offset Current                                                     |                                                                                            |            | • |                          | 0.1              | 15                   |                 | 0.1              | 100            | pA<br>pA                    |

| e <sub>n</sub>           | Input Referred Noise                                                     | f = 1kHz<br>0.1Hz to 10Hz                                                                  |            |   |                          | 13<br>1.3        |                      |                 | 13<br>1.3        |                | nV/√Hz<br>μV <sub>P-P</sub> |

| In                       | Input Noise Current Density (Note 7)                                     |                                                                                            |            |   |                          | 0.5              |                      |                 | 0.5              |                | fA/√Hz                      |

|                          | Input Common Mode Range                                                  |                                                                                            |            | • | V <sup>-</sup>           |                  | V <sup>+</sup>       | V-              |                  | V <sup>+</sup> | V                           |

| C <sub>DIFF</sub>        | Differential Input Capacitance                                           |                                                                                            |            |   |                          | 3                |                      |                 | 3                |                | pF                          |

| C <sub>CM</sub>          | Common Mode Input<br>Capacitance                                         |                                                                                            |            |   |                          | 7                |                      |                 | 7                |                | pF                          |

| CMRR                     | Common Mode Rejection<br>Ratio                                           | V <sub>CM</sub> = 0V to 3.5V<br>V <sub>CM</sub> = 0V to 3.5V<br>V <sub>CM</sub> = 0V to 5V |            | • | 100<br>95<br>86          | 110<br>110<br>95 |                      | 100<br>94<br>86 | 110<br>110<br>95 |                | dB<br>dB<br>dB              |

| PSRR                     | Power Supply Rejection Ratio                                             | V <sub>S</sub> = 2.7V to 5.5V                                                              |            | • | 98<br>96                 | 110              |                      | 98<br>96        | 110              |                | dB<br>dB                    |

| V <sub>OUT</sub>         | Output Voltage, High, Either<br>Output Pin (Referred to V <sup>+</sup> ) | No Load<br> Source = 0.5mA<br> Source = 5mA                                                |            | • | -24<br>-200              | 1                |                      | -25<br>-220     | 1                |                | mV<br>mV<br>mV              |

|                          | Output Voltage, Low, Either<br>Output Pin (Referred to V <sup>-</sup> )  | No Load<br> SINK = 0.5mA<br> SINK = 5mA                                                    |            | • |                          | 1                | 27<br>210            |                 | 1                | 32<br>240      | mV<br>mV<br>mV              |

| A <sub>VOL</sub>         | Large-Signal Voltage Gain                                                | R <sub>LOAD</sub> = 10k, 0.5V < V <sub>OUT</sub> < 4.5V                                    | (          | • | 110                      | 120              |                      | 110             | 120              |                | dB                          |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . Test conditions are $V^+ = 5V$ , $V^- = 0V$ , $V_{CM} = 0.5V$ unless otherwise noted.

|                  |                                                       |                                                      |   | C,         | I SUFFI) | (ES        |            | H SUFFIX | X          |            |

|------------------|-------------------------------------------------------|------------------------------------------------------|---|------------|----------|------------|------------|----------|------------|------------|

| SYMBOL           | PARAMETER                                             | CONDITIONS                                           |   | MIN        | TYP      | MAX        | MIN        | TYP      | MAX        | UNITS      |

| I <sub>SC</sub>  | Output Short-Circuit Current                          | Source<br>Sink                                       | • | 24<br>24   |          |            | 21<br>21   |          |            | mA<br>mA   |

| SR               | Slew Rate                                             | A <sub>V</sub> = 1                                   |   |            | 1        |            |            | 1        |            | V/µs       |

| GBW              | Gain-Bandwidth Product<br>(f <sub>TEST</sub> = 50kHz) | R <sub>L</sub> = 100k                                | • | 2.5<br>1.8 | 3.5      |            | 2.5<br>1.5 | 3.5      |            | MHz<br>MHz |

| $\Phi_0$         | Phase Margin                                          | R <sub>L</sub> = 10k                                 |   |            | 70       |            |            | 70       |            | Deg        |

| $t_S$            | Settling Time 0.1%                                    | A <sub>V</sub> = 1, 1V Step                          |   |            | 6        |            |            | 6        |            | μs         |

| I <sub>S</sub>   | Supply Current<br>(Per Amplifier)                     | No Load                                              | • |            | 340      | 425<br>465 |            | 340      | 425<br>490 | μA<br>μA   |

|                  | Shutdown Current<br>(Per Amplifier)                   | Shutdown, V <sub>SHDN</sub> ≤ 1.2V                   | • |            |          | 6          |            |          |            | μА         |

| $V_S$            | Supply Voltage Range                                  | Guaranteed by the PSRR Test                          | • | 2.7        |          | 5.5        | 2.7        |          | 5.5        | V          |

|                  | Channel Separation                                    | f <sub>S</sub> = 10kHz, R <sub>L</sub> = 10k         |   |            | -120     |            |            | -120     |            | dB         |

|                  | Shutdown Logic                                        | SHDN High<br>SHDN Low                                | • | 3.5        |          | 1.2        | 3.5        |          | 1.2        | V          |

| THD              | Total Harmonic Distortion                             | $f = 10kHz, V^+ = 5V, V_{OUT} = 2V_{P-P}, R_L = 10k$ |   |            | -90      |            |            | -90      |            | dB         |

| t <sub>ON</sub>  | Turn-On Time                                          | V <sub>SHDN</sub> = 1.2V to 3.5V                     |   |            | 10       |            |            | 10       |            | μs         |

| t <sub>OFF</sub> | Turn-Off Time                                         | V <sub>SHDN</sub> = 3.5V to 1.2V                     |   |            | 2        |            |            | 2        |            | μs         |

|                  | SHDN Pin Current                                      | V <sub>SHDN</sub> = 0V                               | • |            |          | 2          |            |          |            | μА         |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** A heat sink may be required to keep the junction temperature below the absolute maximum. This depends on the power supply voltage and how many amplifiers are shorted.

**Note 3:** The LTC6081C/LTC6082C and LTC60811/LTC6082I are guaranteed functional over the operating temperature range of –40°C to 85°C. The LTC6081H/LTC6082H are guaranteed functional over the operating temperature range of –40°C to 125°C.

**Note 4:** The LTC6081C/LTC6082C are guaranteed to meet specified performance from 0°C to 70°C. The LTC6081C/LTC6082C are designed,

characterized and expected to meet specified performance from  $-40^{\circ}$ C to 85°C but are not tested or QA sampled at these temperatures. The LTC6081I/LTC6082I are guaranteed to meet specified performance from  $-40^{\circ}$ C to 85°C. The LTC6081H/LTC6082H are guaranteed to meet specified performance from  $-40^{\circ}$ C to 125°C.

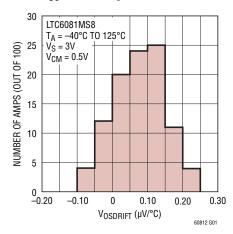

**Note 5:** Input offset drift is computed from the limits of the  $V_{OS}$  test divided by the temperature range. This is a conservative estimate of worst case drift. Consult the Typical Performance Characteristics section for more information on input offset drift.

**Note 6:**  $I_B$  guaranteed by the  $V_S = 5V$  test.

**Note 7:** Current noise is calculated from  $I_n = \sqrt{2qI_B}$ , where  $q = 1.6 \cdot 10^{-19}$  coulomb.

**Note 8:**  $V_{OS}$  drift is guaranteed by the  $V_S$  = 3V test.

LINEAR TECHNOLOGY

#### Vos Drift Histogram

Vos Drift Histogram

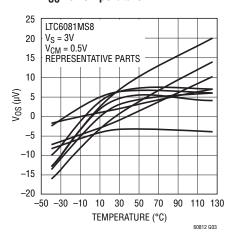

V<sub>OS</sub> vs Temperature

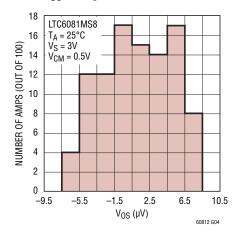

Vos Histogram

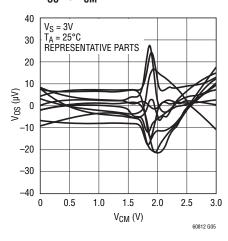

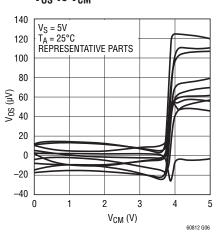

Vos vs V<sub>cm</sub>

Vos vs V<sub>CM</sub>

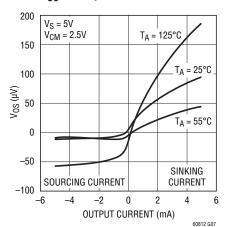

V<sub>OS</sub> vs Output Current

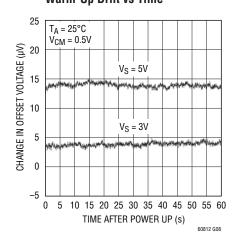

Warm-Up Drift vs Time

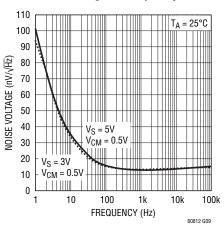

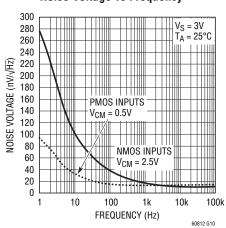

Noise Voltage vs Frequency

Noise Voltage vs Frequency

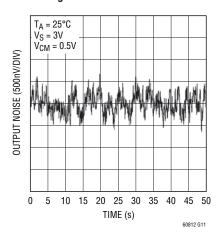

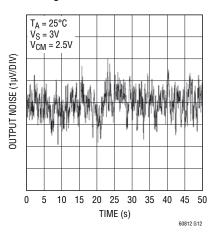

0.1Hz to 10Hz Output Voltage Noise

0.1Hz to 10Hz Output Voltage Noise

**Input Bias Current vs Temperature**

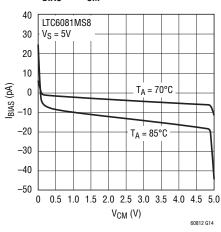

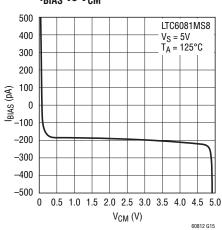

I<sub>BIAS</sub> vs V<sub>CM</sub>

I<sub>BIAS</sub> vs V<sub>CM</sub>

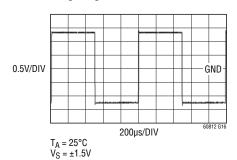

**Large Signal Transient**

$R_L = 10k$

$C_{L}^{-} = 100pF$

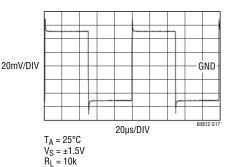

Small Signal Transient

$C_L = 100pF$

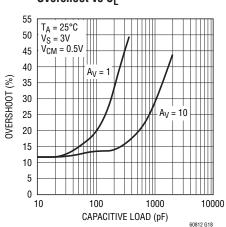

Overshoot vs C<sub>1</sub>

## PIN FUNCTIONS

**OUT:** Amplifier Output

-IN: Inverting Input

+IN: Noninverting Input

V+: Positive Supply

**V**<sup>-</sup>: Negative Supply

**SHDN\_A**: Shutdown Pin of Amplifier A, active low and only valid for LTC6081DD. An internal current source pulls the pin to V<sup>+</sup> when floating.

**SHDN\_B**: Shutdown Pin of Amplifier B, active low and only valid for LTC6081DD. An internal current source pulls the pin to V<sup>+</sup> when floating.

**NC:** Not internally connected.

**Exposed Pad:** Connected to V<sup>-</sup>.

#### APPLICATIONS INFORMATION

#### **Preserving Input Precision**

Preserving input accuracy of the LTC6081/LTC6082 requires that the application circuit and PC board layout do not introduce errors comparable or greater than the 5µV typical offset of the amplifiers. Temperature differentials across the input connections can generate thermocouple voltages of 10's of microvolts so the connections to the input leads should be short, close together and away from heat dissipating components. Air current across the board can also generate temperature differentials.

The extremely low input bias currents (0.1pA typical) allow high accuracy to be maintained with high impedance sources and feedback resistors. Leakage currents on the PC board can be higher than the input bias current. For example,  $10G\Omega$  of leakage between a 5V supply lead and an input lead will generate 500pA! Surround the input leads with a guard ring driven to the same potential as the input common mode voltage to avoid excessive leakage in high impedance applications.

#### **Capacitive Load**

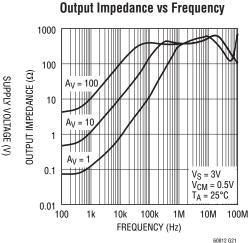

LTC6081/LTC6082 can drive capacitive load up to 200pF in unity gain. The capacitive load driving capability increases as the amplifier is used in higher gain configurations. A small series resistance between the output and the load further increases the amount of capacitance the amplifier can drive.

#### SHDN Pins

Pins 5 and 6 are used for power shutdown on the LTC6081 in the DD package. If they are floating, internal current sources pull Pins 5 and 6 to  $V^+$  and the amplifiers operate normally. In shutdown, the amplifier output is high impedance, and each amplifier draws less than  $2\mu A$  current.

#### Rail-to-Rail Input

The input stage of LTC6081/LTC6082 combines both PMOS and NMOS differential pairs, extending its input common mode voltage range to both positive and negative supply voltages. At high input common mode range, the NMOS pair is on. At low common mode range, the PMOS pair is on. The transition happens when the common voltage is between 1.3V and 0.9V below the positive supply. LTC6081 has better low frequency noise performance with PMOS input on due to its lower flicker noise (see Voltage Noise vs Frequency and 0.1Hz to 10Hz Input Voltage Noise in Typical Performance Characteristics).

#### **Thermal Hysteresis**

Figure 1 shows the input offset voltage hysteresis of the LTC6081IMS8 for 3 thermal cycles from  $-45^{\circ}\text{C}$  to  $90^{\circ}\text{C}$ . The typical offset shift is  $\pm 4\mu\text{V}$ . The data was taken with the ICs in stress free sockets. Mounting to PC boards may cause additional hysteresis due to mechanical stress. The LTC6081 will meet offset voltage specifications in the electrical characteristics table even after  $15\mu\text{V}$  of additional error from thermal hysteresis.

Figure 1.  $V_{OS}$  Thermal Hysteresis of LTC6081MS8

## APPLICATIONS INFORMATION

#### **PC Board Layout**

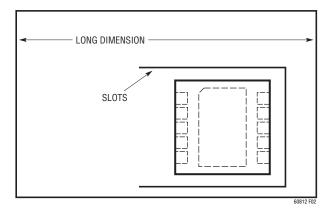

Mechanical stress on a PC board and soldering-induced stress can cause the  $V_{OS}$  and  $V_{OS}$  drift to shift. The DD and DHC packages are more sensitive to stress. A simple way to reduce the stress-related shifts is to mount the IC near the short edge of the PC board, or in a corner. The board edge acts as a stress boundary, or a region where the flexure of the board is minimum. The package should always be mounted so that the leads absorb the stress

and not the package. The package is generally aligned with the leads perpendicular to the long side of the PC board (see Figure 2).

The most effective technique to relieve the PC board stress is to cut slots in the board around the op amp. These slots can be cut on three sides of the IC and the leads can exit on the fourth side. Figure 2 shows the layout of a LTC6081DD with slots at three sides.

Figure 2. Vertical Orientation of LTC6081DD with Slots

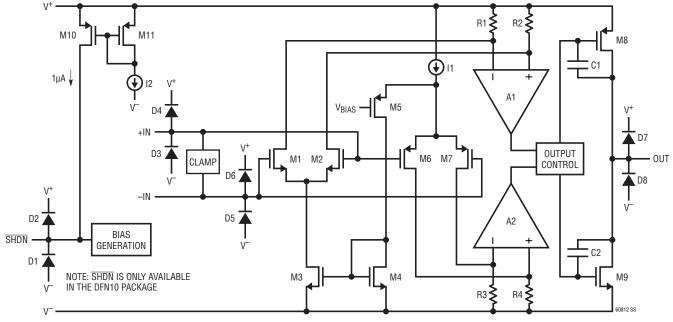

## SIMPLIFIED SCHEMATIC

#### Simplified Schematic of the Amplifier

## TYPICAL APPLICATIONS

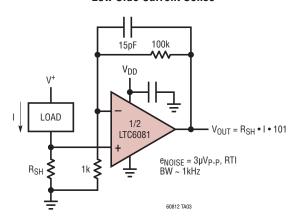

#### **Low Side Current Sense**

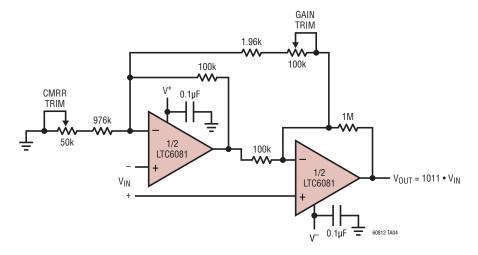

#### Two Op-Amp Instrumentation Amplifier

## TYPICAL APPLICATIONS

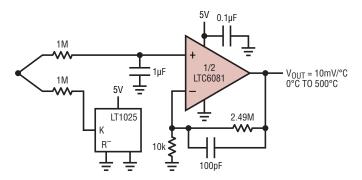

#### Thermocouple Amplifier

SENSOR: OMEGA 5TC-TT-K-30-36 K-TYPE THERMOCOUPLE 1M RESISTORS PROTECT CIRCUIT TO ±350V WITH NO PHASE REVERSAL OF AMPLIFIER OUTPUT 1pA MAX  $I_{BIAS}$  TRANSLATES TO 0.05°C ERROR 20µV  $V_{OS} \rightarrow$  0.5°C OFFSET 60812 TA05

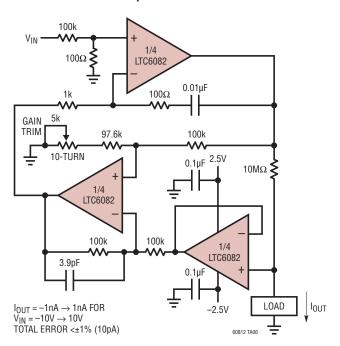

#### **Precision Nanoamp Bidirectional Current Source**

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

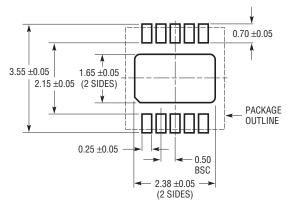

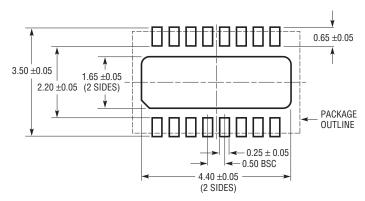

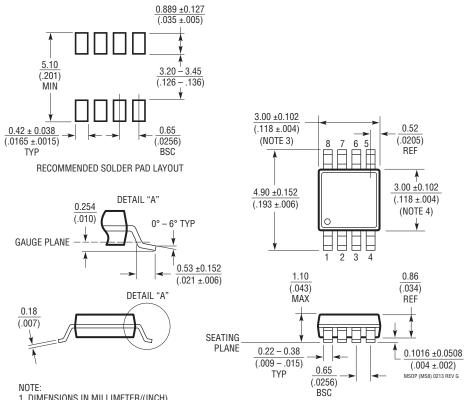

# $\begin{array}{c} \text{DD Package} \\ \text{10-Lead Plastic DFN (3mm} \times \text{3mm)} \end{array}$

(Reference LTC DWG # 05-08-1699 Rev C)

- NOTE

- DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-2).

CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

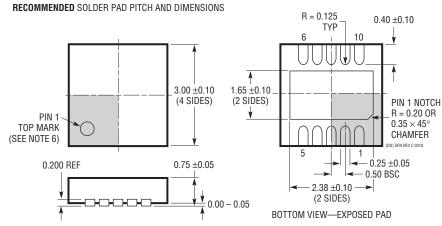

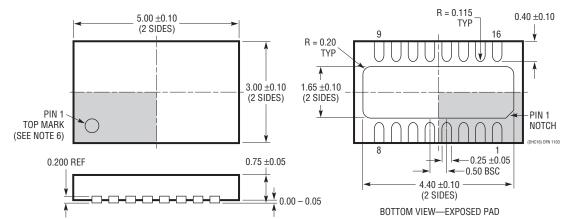

#### **DHC Package** 16-Lead Plastic DFN (5mm × 3mm)

(Reference LTC DWG # 05-08-1706 Rev Ø)

**RECOMMENDED** SOLDER PAD PITCH AND DIMENSIONS

- NOTE:

- 1. DRAWING PROPOSED TO BE MADE VARIATION OF VERSION (WJED-1) IN JEDEC PACKAGE OUTLINE MO-229

- 2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH, MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

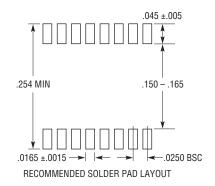

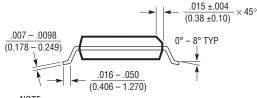

#### GN Package 16-Lead Plastic SSOP (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1641 Rev B)

- NOTE:

- 1. CONTROLLING DIMENSION: INCHES

- 2. DIMENSIONS ARE IN  $\frac{\text{INCHES}}{\text{(MILLIMETERS)}}$

- 3. DRAWING NOT TO SCALE

- 4. PIN 1 CAN BE BEVEL EDGE OR A DIMPLE

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

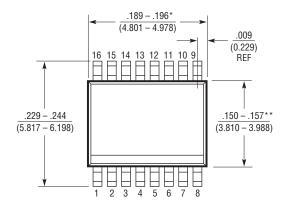

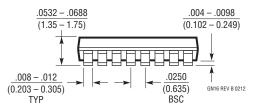

#### **MS8 Package** 8-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1660 Rev G)

- 1. DIMENSIONS IN MILLIMETER/(INCH)

- 2. DRAWING NOT TO SCALE

- DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

# **REVISION HISTORY** (Revision history begins at Rev B)

| REV | DATE  | DESCRIPTION                                                        | PAGE NUMBER |

|-----|-------|--------------------------------------------------------------------|-------------|

| В   | 3/10  | Change LT to LTC on all part numbers in Order Information Section. | 3           |

| С   | 07/10 | Update to Simplified Schematic                                     | 12          |

| D   | 12/13 | Corrected resistor value (10M)                                     | 14          |

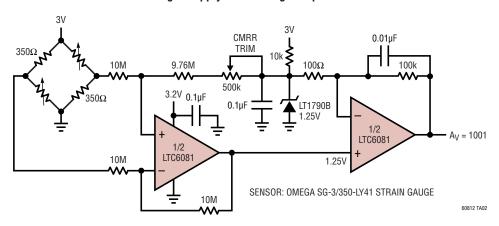

## TYPICAL APPLICATION

#### **Single Supply Strain Gauge Amplifier**

## **RELATED PARTS**

| PART NUMBER     | DESCRIPTION                                | COMMENTS                                          |

|-----------------|--------------------------------------------|---------------------------------------------------|

| LT1678/LT1679   | Dual/Quad Precision Op Amps                | Low Noise, 2.7V to 36V Operation                  |

| LTC2050         | Zero-Drift Op Amp                          | 2.7V Operation, SOT-23 Package                    |

| LTC2051/LTC2052 | Dual/Quad Zero-Drift Op Amps               | MS8/GN16 Packages                                 |

| LTC2054/LTC2055 | Single/Dual Zero-Drift Op Amp              | Micropower, SOT-23 and DFN Packages               |

| LTC6078/LTC6079 | Dual/Quad Low Noise Precision CMOS Op Amps | Micropower 0.7μV/°C V <sub>OS</sub> Drift         |

| LTC6241/LTC6242 | Dual/Quad Low Noise CMOS Op Amps           | 18MHz Bandwidth,10V/µs Slew Rate                  |

| LTC6244         | Dual 50MHz CMOS Op Amp                     | Low Noise, Rail-to-Rail Out, MS8 and DFN Packages |