LTC4151IS-2

### FEATURES

- Wide Operating Voltage Range: 7V to 80V

- 12-Bit Resolution for Both Current and Voltages

- I<sup>2</sup>C Interface

- Additional ADC Input Monitors an External Voltage

- Continuous Scan and Snapshot Modes

- Shutdown Mode (LTC4151) Reduces Quiescent Current to 120µA

- Split SDA for Opto-Isolation (LTC4151-1/LTC4151-2)

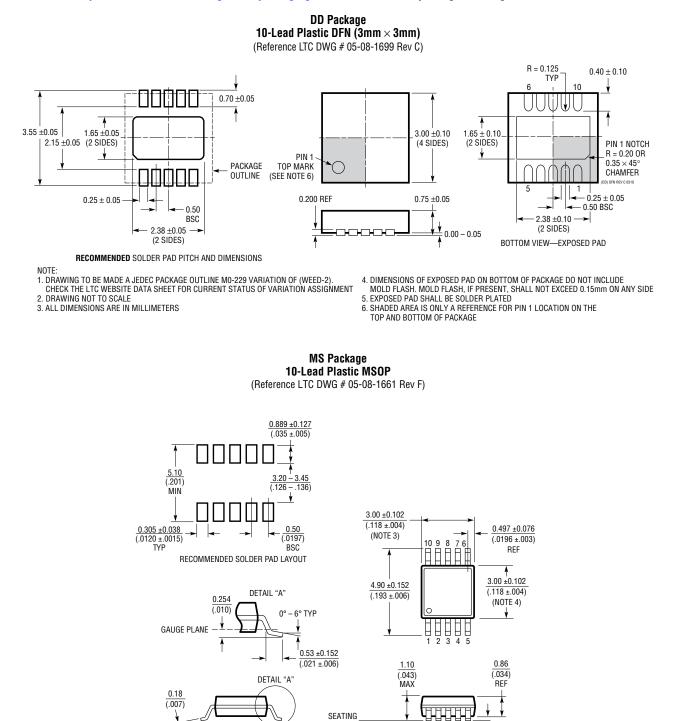

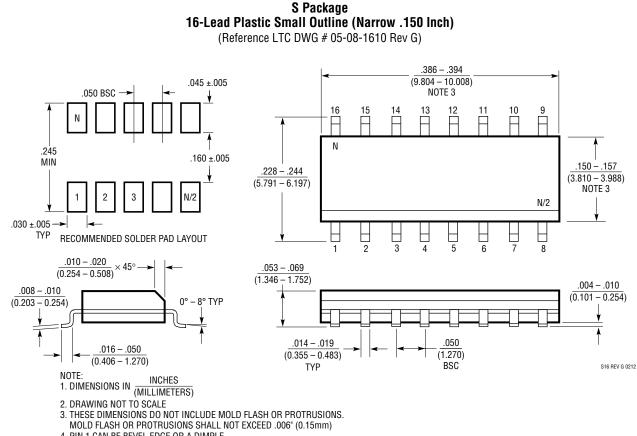

- Available in 10-Lead MSOP, 10-Lead 3mm × 3mm DFN and 16-Lead SO Packages

### **APPLICATIONS**

- –48V Telecom Infrastructure

- Automotive

- Industrial

- Consumer

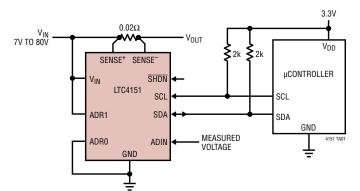

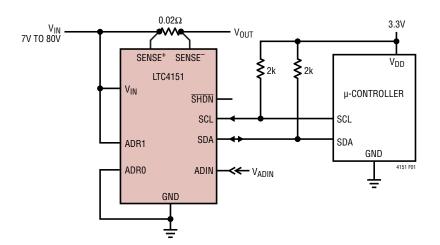

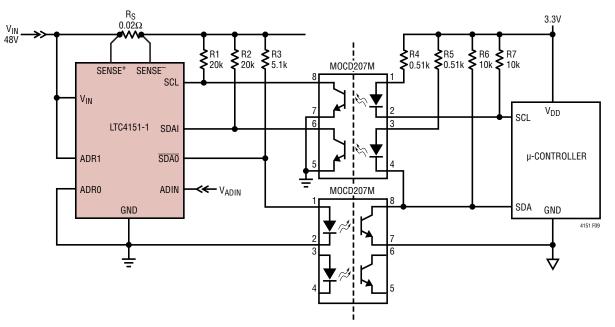

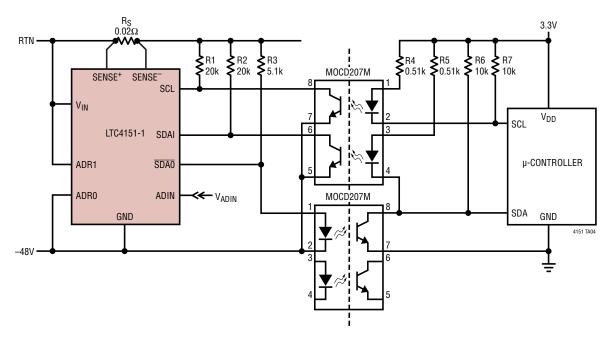

### TYPICAL APPLICATION

## High Voltage I<sup>2</sup>C Current and Voltage Monitor

### DESCRIPTION

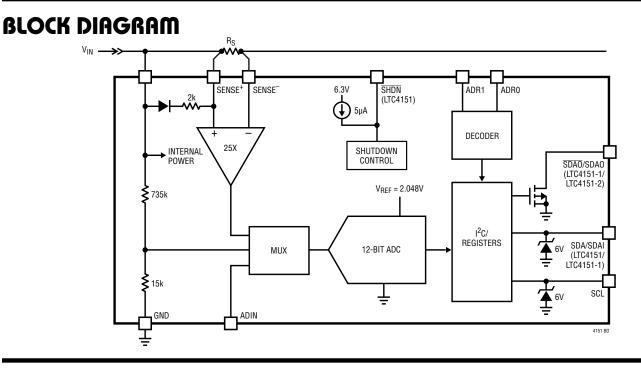

The LTC®4151 is a high side power monitor that operates over a wide voltage range of 7V to 80V. In default operation mode, the onboard 12-bit ADC continuously measures high side current, input voltage and an external voltage. Data is reported through the I<sup>2</sup>C interface when polled by a host. The LTC4151 can also perform on-demand measurement in a snapshot mode. The LTC4151 features a dedicated shutdown pin to reduce power consumption. The LTC4151-1/LTC4151-2 feature split I<sup>2</sup>C data pins to drive opto-isolators. The data out on the LTC4151-1 is inverted while that on the LTC4151-2 is not.

| PART      | PACKAGE    | FEATURED PIN |

|-----------|------------|--------------|

| LTC4151   | DD10, MS10 | SHDN         |

| LTC4151-1 | DD10, MS10 | SDAO         |

| LTC4151-2 | S16        | SDAO         |

∠ , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and Hot Swap is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

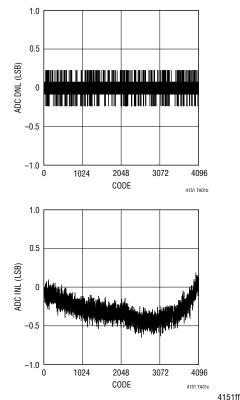

#### 12-Bit ADC DNL and INL

High Side Power Sensing with Onboard ADC and I<sup>2</sup>C

### ABSOLUTE MAXIMUM RATINGS (Notes 1, 3)

| V <sub>IN</sub> Voltage0.3V to 90V                                       | Operat |

|--------------------------------------------------------------------------|--------|

| SENSE <sup>+</sup> , SENSE <sup>-</sup> VoltagesV <sub>IN</sub> – 10V or | LTC    |

| -0.3V to V <sub>IN</sub> + 0.3V                                          | LTC    |

| ADR1, ADR0 Voltages0.3V to 90V                                           | LTC    |

| ADIN, SHDN, SDAO, SDAO Voltages –0.3V to 6V                              | Storag |

| SCL, SDA, SDAI Voltages (Note 2)0.3V to 5.5V                             | MS     |

| SCL, SDA, SDAI Clamp Current 5mA                                         | DFN    |

|                                                                          | Lood   |

| Operating Temperature Range                |

|--------------------------------------------|

| LTC4151C/LTC4151C-1/LTC4151C-2 0°C to 70°C |

| LTC4151I/LTC4151I-1/LTC4151I-240°C to 85°C |

| LTC4151H–40°C to 125°C                     |

| Storage Temperature Range                  |

| MSOP, SO–65°C to 150°C                     |

| DFN–65°C to 125°C                          |

| Lead Temperature (Soldering, 10 sec)       |

| MSOP, SO                                   |

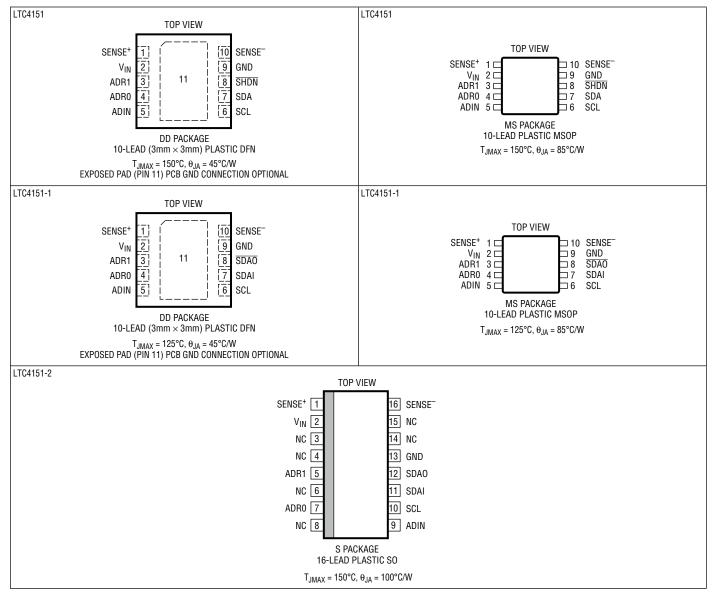

### PIN CONFIGURATION

### ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC4151CDD#PBF   | LTC4151CDD#TRPBF   | LCWZ          | 10-Lead (3mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC4151IDD#PBF   | LTC4151IDD#TRPBF   | LCWZ          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC4151HDD#PBF   | LTC4151HDD#TRPBF   | LCWZ          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LTC4151CDD-1#PBF | LTC4151CDD-1#TRPBF | LCXC          | 10-Lead (3mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC4151IDD-1#PBF | LTC4151IDD-1#TRPBF | LCXC          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC4151CMS#PBF   | LTC4151CMS#TRPBF   | LTCWY         | 10-Lead Plastic MSOP            | 0°C to 70°C       |

| LTC4151IMS#PBF   | LTC4151IMS#TRPBF   | LTCWY         | 10-Lead Plastic MSOP            | -40°C to 85°C     |

| LTC4151HMS#PBF   | LTC4151HMS#TRPBF   | LTCWY         | 10-Lead Plastic MSOP            | -40°C to 125°C    |

| LTC4151CMS-1#PBF | LTC4151CMS-1#TRPBF | LTCXB         | 10-Lead Plastic MSOP            | 0°C to 70°C       |

| LTC4151IMS-1#PBF | LTC4151IMS-1#TRPBF | LTCXB         | 10-Lead Plastic MSOP            | -40°C to 85°C     |

| LTC4151CS-2#PBF  | LTC4151CS-2#TRPBF  | LTC4151S-2    | 16-Lead Plastic SO              | 0°C to 70°C       |

| LTC4151IS-2#PBF  | LTC4151IS-2#TRPBF  | LTC4151S-2    | 16-Lead Plastic SO              | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> is from 7V to 80V, unless noted. (Note 3)

| SYMBOL                | PARAMETER                        | CONDITIONS                                                                                                   |             | MIN | ТҮР                     | MAX                        | UNITS             |

|-----------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------|-------------|-----|-------------------------|----------------------------|-------------------|

| General               | ·                                | ·                                                                                                            |             |     |                         |                            | ·                 |

| V <sub>IN</sub>       | Supply Voltage                   |                                                                                                              |             | 7   |                         | 80                         | V                 |

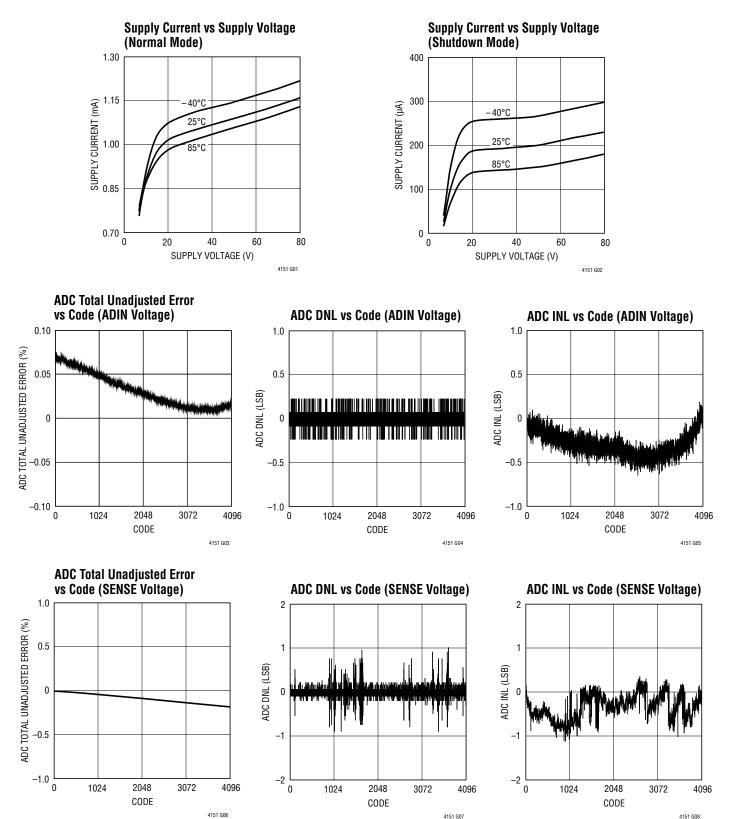

| I <sub>IN</sub>       | Supply Current                   | $V_{IN}$ = 48V, Normal Operation Mode $V_{IN}$ = 12V, Shutdown Mode                                          | •           |     | 1.2<br>120              | 1.7<br>300                 | mA<br>μA          |

| I <sub>SENSE+</sub>   | SENSE <sup>+</sup> Input Current | $V_{IN}$ , SENSE <sup>+</sup> , SENSE <sup>-</sup> = 48V                                                     | •           |     | 5                       | 9                          | μA                |

| I <sub>SENSE</sub> -  | SENSE <sup>-</sup> Input Current | $V_{IN}$ , SENSE <sup>+</sup> , SENSE <sup>-</sup> = 48V                                                     | •           |     | 0.1                     | 1                          | μA                |

| V <sub>SHDN(TH)</sub> | SHDN Input Threshold             |                                                                                                              | •           | 1   | 1.5                     | 2                          | V                 |

| ISHDN                 | SHDN Input Current               | SHDN = 0V                                                                                                    |             | -3  | -5                      | -8                         | μA                |

| ADC                   |                                  | · ·                                                                                                          | · · ·       |     |                         |                            |                   |

| RES                   | Resolution (No Missing Codes)    | (Note 4)                                                                                                     |             | 12  |                         |                            | Bits              |

| V <sub>FS</sub>       | Full-Scale Voltage               | (SENSE <sup>+</sup> – SENSE <sup>-</sup> )<br>V <sub>IN</sub><br>ADIN                                        |             |     | 81.92<br>102.4<br>2.048 |                            | mV<br>V<br>V      |

| LSB                   | LSB Step Size                    | (SENSE <sup>+</sup> – SENSE <sup>-</sup> )<br>V <sub>IN</sub><br>ADIN                                        |             |     | 20<br>25<br>0.5         |                            | μV<br>mV<br>mV    |

| TUE                   | Total Unadjusted Error           | (SENSE <sup>+</sup> – SENSE <sup>-</sup> )<br>V <sub>IN</sub> (Note 5)<br>ADIN, C-Grade<br>ADIN, I-, H-Grade | •<br>•<br>• |     |                         | ±1.25<br>±1<br>±0.75<br>±1 | %<br>%<br>%       |

| V <sub>OS</sub>       | Offset Error                     | (SENSE <sup>+</sup> – SENSE <sup>-</sup> )<br>V <sub>IN</sub> (Note 6)<br>ADIN                               | •           |     |                         | ±5<br>±6<br>±8             | LSB<br>LSB<br>LSB |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> is from 7V to 80V, unless noted. (Note 3)

| SYMBOL                       | PARAMETER                                              | CONDITIONS                                                                     |   | MIN      | ТҮР              | MAX            | UNITS                                                       |

|------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------|---|----------|------------------|----------------|-------------------------------------------------------------|

| INL                          | Integral Nonlinearity                                  | (SENSE <sup>+</sup> – SENSE <sup>-</sup> )<br>V <sub>IN</sub> (Note 5)<br>ADIN | • |          | ±1<br>±1<br>±0.5 | ±3<br>±3<br>±2 | LSB<br>LSB<br>LSB                                           |

| $\sigma_{T}$                 | Transition Noise                                       | (SENSE <sup>+</sup> – SENSE <sup>-</sup> )<br>V <sub>IN</sub><br>ADIN          |   |          | 1.2<br>0.3<br>22 |                | μV <sub>RMS</sub><br>mV <sub>RMS</sub><br>μV <sub>RMS</sub> |

| f <sub>CONV</sub>            | Conversion Rate (Continuous Mode)                      |                                                                                | • | 6        | 7.5              | 9              | Hz                                                          |

| t <sub>CONV</sub>            | Conversion Time (Snapshot Mode)                        | (SENSE <sup>+</sup> – SENSE <sup>-</sup> )<br>ADIN, V <sub>IN</sub>            | • | 53<br>26 | 67<br>33         | 85<br>42       | ms<br>ms                                                    |

| R <sub>ADIN</sub>            | ADIN Pin Input Resistance                              | ADIN = 3V                                                                      | • | 2        | 10               |                | MΩ                                                          |

| I <sub>ADIN</sub>            | ADIN Pin Input Current                                 | ADIN = 3V                                                                      | • |          |                  | ±2             | μA                                                          |

| I <sup>2</sup> C Interface   |                                                        |                                                                                |   |          |                  |                |                                                             |

| V <sub>ADR(H)</sub>          | ADR0, ADR1 Input High Threshold                        |                                                                                | • | 2.3      | 2.65             | 3.0            | V                                                           |

| V <sub>ADR(L)</sub>          | ADRO, ADRI Input Low Threshold                         |                                                                                | • | 0.2      | 0.6              | 0.9            | V                                                           |

| I <sub>ADR(IN)</sub>         | ADRO, ADRI Input Current                               | ADR0, ADR1 = 0V or 3V<br>ADR0, ADR1 = 0.8V or 2.2V                             | • | ±8       |                  | ±70            | μΑ<br>μΑ                                                    |

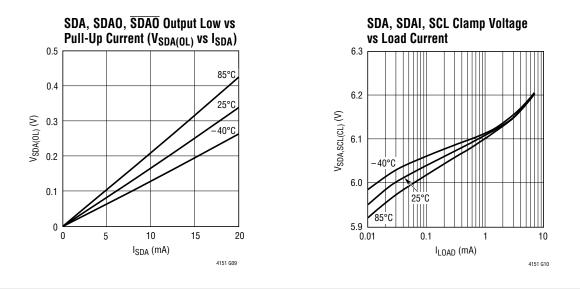

| V <sub>SDA(OL)</sub>         | SDA, SDAO, SDAO Output Low Voltage                     | I <sub>SDA</sub> , I <sub>SDAO</sub> , I <sub>SDAO</sub> = 8mA                 | • |          | 0.15             | 0.4            | V                                                           |

| I <sub>SDA,SCL(IN)</sub>     | SDA, SDAI, SDAO, SDAO, SCL Input<br>Current            | SDA, SDAI, SDAO, <u>SDAO</u> , SCL = 5V                                        | • |          | 0                | ±2             | μA                                                          |

| V <sub>SDA,SCL(TH)</sub>     | SDA, SDAI, SCL Input Threshold                         |                                                                                | • | 1.6      | 1.8              | 2              | V                                                           |

| V <sub>SDA,SCL(CL)</sub>     | SDA, SDAI, SCL Clamp Voltage                           | I <sub>SDA</sub> , I <sub>SDAI</sub> , I <sub>SCL</sub> = 3mA                  | • | 5.5      | 6.1              | 6.6            | V                                                           |

| I <sup>2</sup> C Interface 1 | liming (Note 4)                                        |                                                                                |   |          |                  |                |                                                             |

| f <sub>SCL(MAX)</sub>        | Maximum SCL Clock Frequency                            |                                                                                |   | 400      |                  |                | kHz                                                         |

| t <sub>LOW</sub>             | Minimum SCL Low Period                                 |                                                                                |   |          | 0.65             | 1.3            | μs                                                          |

| t <sub>HIGH</sub>            | Minimum SCL High Period                                |                                                                                |   |          | 50               | 600            | ns                                                          |

| t <sub>BUF(MIN)</sub>        | Minimum Bus Free Time Between Stop/<br>Start Condition |                                                                                |   |          | 0.12             | 1.3            | μs                                                          |

| t <sub>hd,sta(MIN)</sub>     | Minimum Hold Time After (Repeated) Start Condition     |                                                                                |   |          | 140              | 600            | ns                                                          |

| t <sub>SU,STA(MIN)</sub>     | Minimum Repeated Start Condition Set-Up<br>Time        |                                                                                |   |          | 30               | 600            | ns                                                          |

| t <sub>SU,STO(MIN)</sub>     | Minimum Stop Condition Set-Up Time                     |                                                                                |   |          | 30               | 600            | ns                                                          |

| t <sub>HD,DATI(MIN)</sub>    | Minimum Data Hold Time Input                           |                                                                                |   |          | -100             | 0              | ns                                                          |

| t <sub>HD,DATO(MIN)</sub>    | Minimum Data Hold Time Output                          |                                                                                |   | 300      | 600              | 900            | ns                                                          |

| t <sub>SU,DAT(MIN)</sub>     | Minimum Data Set-Up Time Input                         |                                                                                |   |          | 30               | 100            | ns                                                          |

| t <sub>SP(MAX)</sub>         | Maximum Suppressed Spike<br>Pulse Width                |                                                                                |   | 50       | 110              | 250            | ns                                                          |

| t <sub>RST</sub>             | Stuck-Bus Reset Time                                   | SCL or SDA/SDAI Held Low                                                       |   | 20       | 33               |                | ms                                                          |

| C <sub>X</sub>               | SCL, SDA Input Capacitance                             |                                                                                |   |          | 5                | 10             | pF                                                          |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Internal clamps limit the SCL, SDA (LTC4151) and SDAI (LTC4151-1/LTC4151-2) pins to a minimum of 5.5V. Driving these pins to voltages beyond the clamp may damage the part. The pins can be safely tied to higher voltages through a resistor that limits the current below 5mA.

Note 3: All currents into pins are positive. All voltages are referenced to GND, unless otherwise noted.

Note 4: Guaranteed by design and not subject to test.

Note 5: Integral nonlinearity and total unadjusted error of  $V_{\text{IN}}$  are tested between 7V and 80V.

Note 6: Offset error of  $V_{\rm IN}$  is defined by extrapolating the straight line measured between 7V and 80V.

#### **TYPICAL PERFORMANCE CHARACTERISTICS** $V_{IN} = 12V$ , $T_A = 25^{\circ}C$ , unless noted.

### **TYPICAL PERFORMANCE CHARACTERISTICS** $V_{IN} = 12V$ , $T_A = 25^{\circ}C$ , unless noted.

### PIN FUNCTIONS

**ADIN:** ADC Input. The onboard ADC measures voltage range between 0V and 2.048V. Tie to GND if unused.

**ADR1, ADR0:**  $I^2C$  Device Address Inputs. Connecting ADR1 and ADR0 to V<sub>IN</sub>, GND or leaving the pins open configures one of nine possible addresses. See Table 1 in the Applications Information section for details.

**Exposed Pad (DD Package Only):** Exposed pad may be left open or connected to device ground (GND).

GND: Device Ground.

**SCL:**  $I^2C$  Bus Clock Input. Data is shifted in and out at the SDA pin on rising edges of SCL. This pin is driven by an open-collector output from a master controller. An external pull-up resistor or current source is required and can be placed between SCL and V<sub>IN</sub>. The voltage at SCL is internally clamped to 6V (5.5V minimum).

**SDA (LTC4151 Only):** I<sup>2</sup>C Bus Data Input/Output. Used for shifting in address, command or data bits and sending out data. An external pull-up resistor or current source is required and can be placed between SDA and  $V_{IN}$ . The voltage at SDA is internally clamped to 6V (5.5V minimum).

**SDAI (LTC4151-1/LTC4151-2 Only):** I<sup>2</sup>C Bus Data Input. Used for shifting in address, command, data, and SDAO acknowledge bits. This pin is driven by an open-collector output from a master controller. An external pull-up resistor or current source is required and can be placed between SDAI and V<sub>IN</sub>. If the master separates SDAI and SDAO, data read at SDAO needs to be echoed back to SDAI for proper I<sup>2</sup>C communication. The voltage at SDAI is internally clamped to 6V (5.5V minimum).

**SDAO (LTC4151-2 Only):** Serial Bus Data Output. Opendrain output used for sending data back to the master controller or acknowledging a write operation. Normally tied to SDAI to form the SDA line. An external pull-up resistor or current source is required.

**SDAO** (LTC4151-1 Only): Inverted Serial Bus Data Output. Open-drain output used for sending data back to the master controller or acknowledging a write operation. Data is inverted for convenience of opto-isolation. An external pull-up resistor or current source is required.

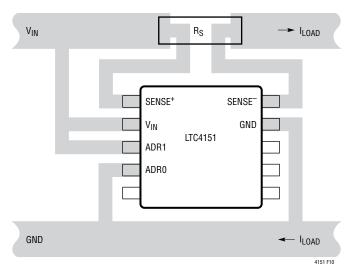

**SENSE+:** Kelvin Sense of the  $V_{\text{IN}}$  Pin. See Figure 10 for recommended Kelvin connection.

**SENSE<sup>-</sup>:** High Side Current Sense Input. Connect an external sense resistor between SENSE<sup>+</sup> and SENSE<sup>-</sup>. The differential voltage between SENSE<sup>+</sup> and SENSE<sup>-</sup> is monitored by the onboard ADC with a full-scale sense voltage of 81.92mV.

### PIN FUNCTIONS

**SHDN** (LTC4151 Only): Shutdown Input. Internally pulled up to 6.3V. Pull this pin below 1V to force the LTC4151 into shutdown mode. Leave this pin open if unused.

$V_{\text{IN}}$ : Supply Voltage Input. Accepts 7V to 80V. The voltage at this pin is monitored by the onboard ADC with a full-scale input range of 102.4V. SENSE<sup>+</sup> must be connected to V<sub>IN</sub> for proper ADC readout.

### OPERATION

The LTC4151 accurately monitors high side current and voltages. This device accepts a wide range of input voltages from as low as 7V up to 80V and consumes less than 1.7mA quiescent current in normal operation. A shutdown mode is available with the LTC4151 to reduce the quiescent current to less than 300µA by pulling the SHDN pin below 1V.

In default continuous scan mode after power-up, the onboard 12-bit analog-to-digital converter (ADC) continuously and sequentially measures the high side differential voltage between SENSE<sup>+</sup> (Kelvin sense of V<sub>IN</sub>) and SENSE<sup>-</sup> (full-scale 81.92mV) through an internal sense amplifier, the input voltage V<sub>IN</sub> (full-scale 102.4V) through an internal voltage divider, and the voltage applied to the ADIN pin (full-scale 2.048V). The reference voltage of the ADC is internally set to 2.048V. The digital data obtained by the ADC is stored in the onboard registers.

In snapshot mode, the LTC4151 can perform on-demand measurement of a selected voltage without the need of continuous polling by a master controller. The snapshot mode is enabled by programming the control register through the I<sup>2</sup>C interface. A status bit in the data register monitors the ADC's conversion. When the conversion is completed, the 12-bit digital code of the measured voltage is held in the corresponding data registers.

The LTC4151 provides an I<sup>2</sup>C interface to read the ADC data from the data registers and to program the control register. Two three-state pins, ADR0 and ADR1, are used to decode nine device addresses (see Table 1). The LTC4151 features a single SDA pin to handle both input data and output data, while the LTC4151-1/LTC4151-2 provide separate data in (SDAI) and data out (SDAO on the LTC4151-1 and SDAO on the LTC4151-2) pins to facilitate opto-isolation.

The LTC4151 offers a compact complete solution for high side power monitoring. With a wide operating voltage range from 7V to 80V, this device is ideal for a variety of applications including consumer, automotive, industrial and telecom infrastructure. The simple application circuit as shown in Figure 1 provides monitoring of high side current with a 0.02 $\Omega$  resistor (4.096A in full scale), input voltage (102.4V in full scale) and an external voltage (2.048V in full scale), all with an internal 12-bit resolution ADC.

#### Data Converter

The LTC4151 features an onboard, 12-bit  $\Delta\Sigma$  A/D converter (ADC) that continuously monitors three voltages in the sequence of (V<sub>SENSE+</sub> – V<sub>SENSE</sub>) first, V<sub>IN</sub> second and V<sub>ADIN</sub> third. The  $\Delta\Sigma$  architecture inherently averages signal noise during the measurement period. The differential voltage between SENSE<sup>+</sup> and SENSE<sup>-</sup> is monitored with an 81.92mV full scale and 20µV resolution that allows accurate measurement of the high side input current. SENSE<sup>+</sup> is a Kelvin sense pin for the V<sub>IN</sub> pin and must be connected to V<sub>IN</sub> (see Figure 10) for proper ADC readout. The supply voltage at V<sub>IN</sub> is directly measured with a 102.4V full scale and 25mV resolution. The voltage at the uncommitted ADIN pin is measured with a 2.048V full scale and 0.5mV resolution that allows monitoring of any external voltage. The 12-bit digital

code of each measured voltage is stored in two adjacent registers out of the six total data registers A through F, with the eight MSBs in the first register and the four LSBs in the second (Table 2).

The data in registers A through F is refreshed at a frequency of 7.5Hz in continuous scan mode. Setting control register bit G4 (Table 6) invokes a test mode that halts updating of these registers so that they can be written to and read from for software testing.

The data converter features a snapshot mode allowing users to make one-time measurements of a selected voltage (either the SENSE voltage,  $V_{IN}$  voltage, or ADIN voltage). To enable snapshot mode, set control register bit G7 and write the 2-bit code of the desired ADC channel to G6 and G5 (Table 6) using a Write Byte command. When the Write Byte command is completed, the ADC measures the selected voltage and a Busy Bit in the LSB data register is set to indicate that the data is not ready. After completing the conversion, the ADC is halted and the Busy Bit is reset to indicate that the data is ready. To make another measurement of the same voltage or to measure another voltage, first disable the snapshot mode for the previous measurement by clearing control bit G7, then re-enable the snapshot mode and write the code of the desired voltage according to the procedure described above. The Busy Bit remains reset in the continuous scan mode.

Figure 1. Monitoring High Side Current and Voltages Using the LTC4151

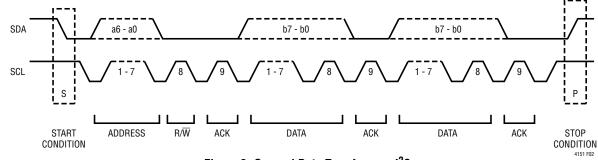

#### I<sup>2</sup>C Interface

The LTC4151 features an I<sup>2</sup>C-compatible interface to provide access to six ADC data registers and a control register for monitoring the measured voltages. Figure 2 shows a general data transfer format using the I<sup>2</sup>C. The LTC4151 is a read-write slave device and supports SMBus Read Byte, Write Byte, Read Word and Write Word commands. The device also supports Read Page and Write Page commands that allow one to read or write more than two bytes of data. When using the Read Page and Write

Page commands, the host need only to issue an initial register address and the internal register address pointer automatically increments by 1 after each byte of data is read or written. After the register address reaches 06h, it will be reset to 00h and continue the increment. Upon a Stop condition, the register address is reset to 00h. If desired, the Read Page and Write Page support can be disabled by clearing control register bit G3. The data formats for the above commands are shown in Figures 3 to 8.

Figure 2. General Data Transfer over I<sup>2</sup>C

S ADDRESS W A

| S | ADDRESS                    | W | A | COM  | MAND                           | A   | DATA  | A  | P |

|---|----------------------------|---|---|------|--------------------------------|-----|-------|----|---|

|   | 1 1 0 a3:a0                | 0 | 0 | ХХХХ | X b2:b0                        | 0   | b7:b0 | 0  |   |

|   | ] FROM MAST<br>] FROM SLAV |   |   |      | A: ACKN<br>Ā: Not A<br>R: Read | ACK | NOWLE | DG |   |

Figure 3. LTC4151 Serial Bus SDA Write Byte Protocol

| ADDRESS     | W | A | COMMAND           | A | DATA  | A | DATA  | A | <br>DATA  | A | Ρ | S |   |

|-------------|---|---|-------------------|---|-------|---|-------|---|-----------|---|---|---|---|

| 1 1 0 a3:a0 | 0 | 0 | X X X X X X b2:b0 | 0 | b7:b0 | 0 | b7:b0 | 0 | <br>b7:b0 | 0 |   |   | 1 |

| 1 1 0 a3:a0 | 0 | 0 | X X X X X b2:b0 | 0 | b7:b0 | 0 | b7:b0 | 0   |        |

|-------------|---|---|-----------------|---|-------|---|-------|-----|--------|

|             |   |   |                 |   |       |   |       | 415 | 51 F04 |

| <br>        |   |   | 0 · · D 0/      |   |       |   |       |     |        |

COMMAND

A DATA A DATA A P

Figure 4. LTC4151 Serial Bus SDA Write Word Protocol

|   | ADDRESS     | vv | A | COMMAND           | A | S | ADDRESS     | R | A | DATA  | A | Ρ |

|---|-------------|----|---|-------------------|---|---|-------------|---|---|-------|---|---|

| 1 | l 1 0 a3:a0 | 0  | 0 | X X X X X X b2:b0 | 0 |   | 1 1 0 a3:a0 | 1 | 0 | b7:b0 | 1 |   |

Figure 5. LTC4151 Serial Bus SDA Write Page Protocol

Figure 6. LTC4151 Serial Bus SDA Read Byte Protocol

| S        | ADDRESS     | W | A | COMMAND           | A | S | ADDRESS     | R | A | DATA  | A | DATA  | Ā | Р |

|----------|-------------|---|---|-------------------|---|---|-------------|---|---|-------|---|-------|---|---|

|          | 1 1 0 a3:a0 | 0 | 0 | X X X X X X b2:b0 | 0 |   | 1 1 0 a3:a0 | 1 | 0 | b7:b0 | 0 | b7:b0 | 1 |   |

| 4151 F07 |             |   |   |                   |   |   |             |   |   |       |   |       |   |   |

Figure 7. LTC4151 Serial Bus SDA Read Word Protocol

| S | ADDRESS     | W | A | COMMAND           | A | S | ADDRESS     | R | A | DATA  | A | DATA  | <br>DATA  | Ā | Ρ |

|---|-------------|---|---|-------------------|---|---|-------------|---|---|-------|---|-------|-----------|---|---|

|   | 1 1 0 a3:a0 | 0 | 0 | X X X X X X b2:b0 | 0 |   | 1 1 0 a3:a0 | 1 | 0 | b7:b0 | 0 | b7:b0 | <br>b7:b0 | 1 |   |

Figure 8. LTC4151 Serial Bus SDA Read Page Protocol

#### Using Opto-Isolators with LTC4151-1 and LTC4151-2

The LTC4151-1/LTC4151-2 split the SDA line into SDAI (input) and SDAO (LTC4151-1 inverted output) or SDAO (LTC4151-2 output) for convenience of opto-coupling with a host controller that sits at a different ground level.

When using opto-isolators with the LTC4151-1, connect the SDAI to the output of the incoming opto-coupler and connect the SDAO to the anode of the outgoing optocoupler (see Figure 9). With the outgoing opto-coupler clamping SDAO and internal 6V (5.5V minimum) clamps on SDAI and SCL, the pull-up resistors on these three pins can be directly connected to V<sub>IN</sub>. In this way (with SDAO rather than conventional SDAO), the need for a separate low voltage supply for pull-ups is eliminated.

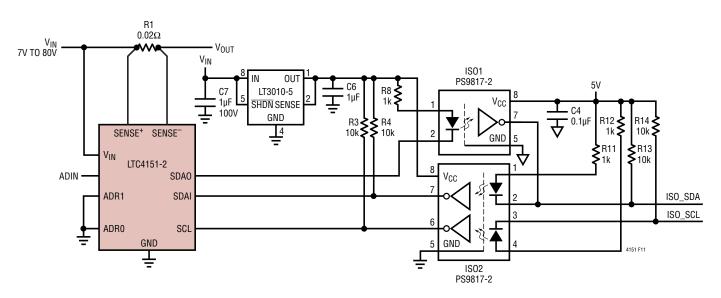

Figure 11 shows the LTC4151-2 with high speed optocouplers for faster bus speeds. The LTC4151-2 has a noninverter SDAO output. Powered from  $V_{IN}$ , the high voltage LT3010-5 low dropout regulator provides the supply for the opto-couplers as well as the bus lines pull-up. If the SDAI and SDAO on the master controller are not tied together, the ACK bit of the SDAO must be returned back to SDAI.

#### **Start and Stop Conditions**

When the I<sup>2</sup>C bus is idle, both SCL and SDA must remain in the high state. A bus master signals the beginning of a transmission with a Start condition by transitioning SDA from high to low while SCL stays high. When the master has finished communicating with the slave, it issues a Stop condition by transitioning SDA from low to high while SCL stays high. The bus is then free for another transmission.

#### **Stuck-Bus Reset**

The LTC4151 I<sup>2</sup>C interface features a stuck-bus reset timer. The low conditions of the SCL and the SDA/SDAI pins are OR'ed to start the timer. The timer is reset when both SCL and SDA/SDAI are pulled high. If the SCL pin or the SDA/SDAI pin is held low for over 33ms, the stuck-bus timer will expire and the internal I<sup>2</sup>C state machine will be reset to allow normal communication after the stuck-bus condition is cleared. The stuck-bus timer can be disabled by clearing control register bit G2.

Figure 9. Opto-Isolation of the I<sup>2</sup>C Interface Between LTC4151-1 and a Microcontroller (1.5kHz Data Rate of I<sup>2</sup>C is Limited by Slew Rate of Opto-Isolators)

#### I<sup>2</sup>C Device Addressing

Nine distinct I<sup>2</sup>C bus addresses are configurable using the three-state pins ADR0 and ADR1, as shown in Table 1. Address bits a6, a5 and a4 are configured to (110) and the least significant bit is the  $R/\overline{W}$  bit. In addition, the LTC4151 will respond to a mass write address (1100 110) b for writing to all LTC4151s, regardless of their individual address settings.

#### Acknowledge

The acknowledge signal is used for handshaking between the transmitter and the receiver to indicate that the last byte of data was received. The transmitter always releases the SDA line during the acknowledge clock pulse. The LTC4151 pulls the SDA line low on the 9th clock cycle to acknowledge receipt of the data. If the slave fails to acknowledge by leaving SDA high, then the master can abort the transmission by generating a Stop condition. When the master is receiving data from the slave, the master must pull down the SDA line during the clock pulse to indicate receipt of a data byte, and that another byte is to be read. After the last byte has been received the master will leave the SDA line high (not acknowledge) and issue a Stop condition to terminate the transmission.

### Write Protocol

The master begins a write operation with a Start condition followed by the seven bit slave address and the  $R/\overline{W}$  bit

set to zero. After the addressed LTC4151 acknowledges the address byte, the master then sends a command byte which indicates which internal register the master wishes to write. The LTC4151 acknowledges this and then latches the lower three bits of the command byte into its internal register address pointer. The master then delivers the data byte and the LTC4151 acknowledges once more and latches the data into its internal register. If the master continues sending a second byte or more data bytes, as in a Write Word or Write Page command, the second byte or more data bytes will be acknowledged by the LTC4151, the internal register address pointer will increment automatically, and each byte of data will be latched into an internal register corresponding to the address pointer. The write operation terminates and the register address pointer resets to 00h when the master sends a Stop condition.

#### **Read Protocol**

The master begins a read operation with a Start condition followed by the seven bit slave address and the  $R/\overline{W}$  bit set to zero. After the addressed LTC4151 acknowledges the address byte, the master then sends a command byte that indicates which internal register the master wishes to read. The LTC4151 acknowledges this and then latches the lower three bits of the command byte into its internal register address pointer. The master then sends a repeated Start condition followed by the same seven bit

| DESCRIPTION | HEX DEVICE<br>ADDRESS | BINARY DEVICE ADDRESS |    |    |    |    |    | LTC4151<br>Address Pins |     |      |      |

|-------------|-----------------------|-----------------------|----|----|----|----|----|-------------------------|-----|------|------|

|             | h                     | a6                    | a5 | a4 | a3 | a2 | a1 | a0                      | R/W | ADR1 | ADRO |

| Mass Write  | CC                    | 1                     | 1  | 0  | 0  | 1  | 1  | 0                       | 0   | Х    | Х    |

| 0           | CE                    | 1                     | 1  | 0  | 0  | 1  | 1  | 1                       | Х   | Н    | L    |

| 1           | D0                    | 1                     | 1  | 0  | 1  | 0  | 0  | 0                       | Х   | NC   | Н    |

| 2           | D2                    | 1                     | 1  | 0  | 1  | 0  | 0  | 1                       | Х   | Н    | Н    |

| 3           | D4                    | 1                     | 1  | 0  | 1  | 0  | 1  | 0                       | Х   | NC   | NC   |

| 4           | D6                    | 1                     | 1  | 0  | 1  | 0  | 1  | 1                       | Х   | NC   | L    |

| 5           | D8                    | 1                     | 1  | 0  | 1  | 1  | 0  | 0                       | Х   | L    | Н    |

| 6           | DA                    | 1                     | 1  | 0  | 1  | 1  | 0  | 1                       | Х   | Н    | NC   |

| 7           | DC                    | 1                     | 1  | 0  | 1  | 1  | 1  | 0                       | Х   | L    | NC   |

| 8           | DE                    | 1                     | 1  | 0  | 1  | 1  | 1  | 1                       | Х   | L    | L    |

Table 1. LTC4151 Device Addressing\*

\*H = Tie High; L = Tie to GND; NC = Open; X = Don't Care

#### Table 2. LTC4151 Register Address and Contents

| REGISTER ADDRESS* | REGISTER NAME       | READ/WRITE | DESCRIPTION                               |

|-------------------|---------------------|------------|-------------------------------------------|

| 00h               | SENSE (A)           | R/W**      | ADC Current Sense Voltage Data (8 MSBs)   |

| 01h               | SENSE (B)           | R/W**      | ADC Current Sense Voltage Data (4 LSBs)   |

| 02h               | V <sub>IN</sub> (C) | R/W**      | ADC V <sub>IN</sub> Voltage Data (8 MSBs) |

| 03h               | V <sub>IN</sub> (D) | R/W**      | ADC V <sub>IN</sub> Voltage Data (4 LSBs) |

| 04h               | ADIN (E)            | R/W**      | ADC ADIN Voltage Data (8 MSBs)            |

| 05h               | ADIN (F)            | R/W**      | ADC ADIN Voltage Data (4 LSBs)            |

| 06h               | CONTROL (G)         | R/W        | Controls ADC Operation Mode and Test Mode |

| 07h               | Reserved            |            |                                           |

\*Register address MSBs b7-b3 are ignored. \*\*Writable if bit G4 is set.

#### Table 3. SENSE Registers A (00h) and B (01h)-Read/Write

| BIT        | NAME                      | OPERATION                                                                        |  |

|------------|---------------------------|----------------------------------------------------------------------------------|--|

| A7:0, B7:4 | SENSE Voltage Data        | 12-Bit Data of Current Sense Voltage with $20\mu V$ LSB and $81.92mV$ Full-Scale |  |

| B3         | ADC Busy in Snapshot Mode | 1 = SENSE Being Converted; 0 = SENSE Conversion Completed. Not Writable          |  |

| B2:0       | Reserved                  | Always Returns 0. Not Writable                                                   |  |

#### Table 4. $V_{\mbox{\scriptsize IN}}$ Registers C (02h) and D (03h)—Read/Write

| BIT        | NAME                         | DPERATION                                                                     |  |  |

|------------|------------------------------|-------------------------------------------------------------------------------|--|--|

| C7:0, D7:4 | V <sub>IN</sub> Voltage Data | 12-Bit Data of V <sub>IN</sub> Voltage with 25mV LSB and 102.4V Full-Scale    |  |  |

| D3         | ADC Busy in Snapshot Mode    | $1 = V_{IN}$ Being Converted; $0 = V_{IN}$ Conversion Completed. Not Writable |  |  |

| D2:0       | Reserved                     | Always Returns 0, Not Writable                                                |  |  |

#### Table 5. ADIN Registers E (04h) and F (05h)-Read/Write

| BIT        | NAME                      | OPERATION                                                                      |

|------------|---------------------------|--------------------------------------------------------------------------------|

| E7:0, F7:4 | ADIN Voltage Data         | 12-Bit Data of Current Sense Voltage with $500\mu V$ LSB and 2.048V Full-Scale |

| F3         | ADC Busy in Snapshot Mode | 1 = ADIN Being Converted; 0 = ADIN Conversion Completed. Not Writable          |

| F2:0       | Reserved                  | Always Returns 0, Not Writable                                                 |

#### Table 6. CONTROL Register G (06h)-Read/Write

| BIT  | NAME                                   | OPERATION                                                                                                                                                                                                                                                  |  |  |  |

|------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| G7   | ADC Snapshot Mode<br>Enable            | Enables ADC Snapshot Mode; 1 = Snapshot Mode Enabled. Only the channel selected by G6 and G5 is measured by the ADC. After the conversion, the channel busy bit is reset and the ADC is halted.<br>0 = Snapshot Mode Disabled (ADC free running, Default). |  |  |  |

| G6   | ADC Channel Label for<br>Snapshot Mode | ADC Channel Label for Snapshot Mode                                                                                                                                                                                                                        |  |  |  |

| G5   | ADC Channel Label for<br>Snapshot Mode | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                     |  |  |  |

| G4   | Test Mode Enable                       | Test Mode Halts ADC Operation and Enables Writes to ADC Registers; 1 = Enable Test Mode,<br>0 = Disable Test Mode (Default)                                                                                                                                |  |  |  |

| G3   | Page Read/Write Enable                 | Enables Page Read/Write; 1 = Enable I <sup>2</sup> C Page Read/Write (Default), 0 = Disable I <sup>2</sup> C Page Read/Write                                                                                                                               |  |  |  |

| G2   | Stuck-Bus Timer Enable                 | Enables I <sup>2</sup> C Stuck-Bus Reset Timer; 1 = Enable Stuck-Bus Timer (Default), 0 = Disable Stuck-Bus Timer                                                                                                                                          |  |  |  |

| G1:0 | Reserved                               | Always Returns 0, Not Writable                                                                                                                                                                                                                             |  |  |  |

|      |                                        | 4151f                                                                                                                                                                                                                                                      |  |  |  |

address with the R/W bit now set to one. The LTC4151 acknowledges and sends the contents of the requested register. The transmission terminates when the master sends a Stop condition. If the master acknowledges the transmitted data byte, as in a Read Word command, the LTC4151 will send the contents of the next register. If the master acknowledges the second data byte and each of the following (if more) data bytes, as in a Read Page command, the LTC4151 will keep sending out each data byte in the register that corresponds to the incrementing register pointer. The read operation terminates and the register address pointer resets to 00h when the master sends a Stop condition.

#### **Layout Considerations**

A Kelvin connection between the sense resistor  $R_S$  and the LTC4151 is recommended to achieve accurate current sensing (Figure 10). The minimum trace width for 1oz copper foil is 0.02" per amp to make sure the trace

stays at a reasonable temperature. Using 0.03" per amp or wider is recommended. Note that 1oz copper exhibits a sheet resistance of about  $530\mu\Omega$  per square.

Figure 10. Recommended Layout for Kelvin Connection

Figure 11. LTC4151-2 I<sup>2</sup>C Opto-Isolation Interface with High Speed Opto-Couplers

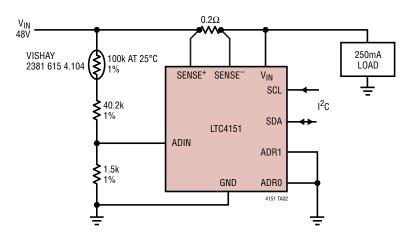

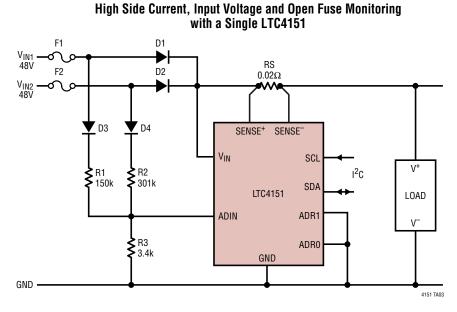

### TYPICAL APPLICATION

Temperature Monitoring with an NTC Thermistor While Measuring Load Current and LTC4151 Supply Current

$\label{eq:total_total_states} \begin{array}{l} T(^{\circ}C) = 58.82 \bullet (N_{ADIN}/N_{VIN} - 0.1066), \ 20^{\circ}C < T < 60^{\circ}C. \\ N_{ADIN} \ \text{AND} \ N_{VIN} \ \text{ARE DIGITAL CODES MEASURED BY THE} \\ \text{ADC AT THE ADIN AND } V_{IN} \ \text{PINS, RESPECTIVELY.} \end{array}$

LTC4151-1 Monitors Current and Input Voltage of a –48V System and Interfaces with a Microcontroller (1.5kHz Data Rate of  $I^2C$  is Limited by Slew Rate of Opto-Isolators)

### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

- NOTE

- 1. DIMENSIONS IN MILLIMETER/(INCH) 2. DRAWING NOT TO SCALE

- DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

PLANE

0.17 - 0.27

(.007 - .011)

TYP

0.50

(.0197)

BSC

0.1016 ±0.0508

(.004 ±.002)

MSOP (MS) 0213 REV F

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

4. PIN 1 CAN BE BEVEL EDGE OR A DIMPLE

### **REVISION HISTORY** (Revision history begins at Rev C)

| REV | DATE  | DESCRIPTION                                                                          | PAGE NUMBER |

|-----|-------|--------------------------------------------------------------------------------------|-------------|

| С   | 11/10 | Added H-grade information                                                            | 2, 3        |

|     |       | Revised order of Pin Functions section and added information to SDAI pin description | 6           |

|     |       | Added diode and 2k resistor to Block Diagram                                         | 7           |

|     |       | Added information to Application Information section                                 | 10          |

| D   | 7/12  | Changed part number in Pin Configuration section from LT4151 to LTC4151              | 2           |

| E   | 11/12 | Added –48V application schematic                                                     | 14          |

| F   | 3/14  | Increased V <sub>ADR(H)</sub> MAX limit and decreased V <sub>ADR(L)</sub> MIN limit  | 4           |

### TYPICAL APPLICATION

| CONDITION                                                     | RESULT                  |

|---------------------------------------------------------------|-------------------------|

| $N_{ADIN} \geq 1.375 \bullet N_{VIN}$                         | Normal Operation        |

| $0.835 \bullet N_{VIN} \leq N_{ADIN} < 1.375 \bullet N_{VIN}$ | F2 is Open              |

| $0.285 \bullet N_{VIN} \leq N_{ADIN} < 0.835 \bullet N_{VIN}$ | F1 is Open              |

| (Not Responding)                                              | Both F1 and F2 are Open |

$V_{\rm IN1}$  and  $V_{\rm IN2}$  are within 20% apart.  $N_{ADIN}$  and  $N_{VIN}$  are digital codes measured by the ADC at the ADIN and  $V_{\rm IN}$  pins, respectively.

### **RELATED PARTS**

8

Linear Technology Corporation 1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 • FAX: (408) 434-0507 • www.linear.com/LTC4151

| PART NUMBER           | DESCRIPTION                                                             | COMMENTS                                                                                               |  |

|-----------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| LT2940                | Power and Current Monitor                                               | Four-Quadrant Multiplication, ±5% Power Accuracy, 4V to 80V Operation                                  |  |

| LTC2945               | Wide Range I <sup>2</sup> C Power Monitor                               | 0V to 80V Input Range, 2.7V to 80V Supply Range, Shunt Regulator, 12-Bit ADC with $\pm 0.75\%$ TUE     |  |

| LTC2451               | 16-Bit I <sup>2</sup> C Ultra Tiny Delta Sigma ADC                      | Single-Ended Input, 0 to $V_{\mbox{CC}}$ Input Range, 60Hz Output Rate, 3mm $\times$ 2mm DFN-8 Package |  |

| LTC2453               | 16-Bit I <sup>2</sup> C Ultra Tiny Delta Sigma ADC                      | Differential Input, ±V <sub>CC</sub> Input Range, 60Hz Output Rate, 3mm × 2mm<br>DFN-8 Package         |  |

| LTC2970               | Power Supply Monitor and Margining Controller                           | 14-Bit ADC Monitoring Current and Voltages, Supplies from 8V to 15V                                    |  |

| LTC4215               | Positive Hot Swap <sup>™</sup> Controller with ADC and I <sup>2</sup> C | 8-Bit ADC Monitoring Current and Voltages, Supplies from 2.9V to 15V                                   |  |

| LTC4260               | Positive High Voltage Hot Swap Controller with ADC and I <sup>2</sup> C | 8-Bit ADC Monitoring Current and Voltages, Supplies from 8.5V to 80V                                   |  |

| LTC4261/<br>LTC4261-2 | Negative High Voltage Hot Swap Controller with ADC and I <sup>2</sup> C | 10-Bit ADC Monitoring Current and Voltages, Supplies from –12V                                         |  |

| LTC6101/<br>LTC6101HV | High Voltage, High Side Current Sense Amplifier<br>in SOT-23 Package    | Supplies from 4V to 60V (LTC6101) and 5V to 100V (LTC6101HV)                                           |  |