Y Dual Multitopology DC/DC Converters with 2A Switches and Synchronization

### FEATURES

- Dual 2A and One 500mA, 50V Internal Power Switch Channels

- 2A Primary Channels Can Be Buck, Boost, SEPIC, ZETA, Flyback or Inverting DC/DC Converter

- 500mA Skyhook Channel Efficiently Generates Boosted Input Voltage

- Wide Input Voltage Range of 2.6V to 50V

- UVLO and OVLO Programmable on OV/UV Pin

- Soft-Start Programmable for Each Channel

- Fixed Frequency PWM (Set by RT Pin or Synchronized to External Clock)

- Anti-Phase Switching Reduces Input Ripple

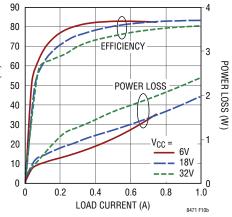

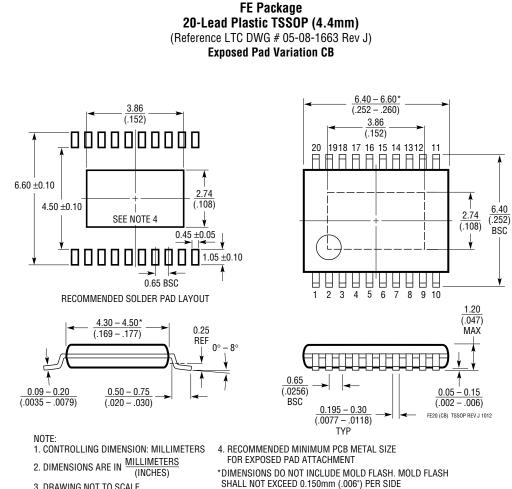

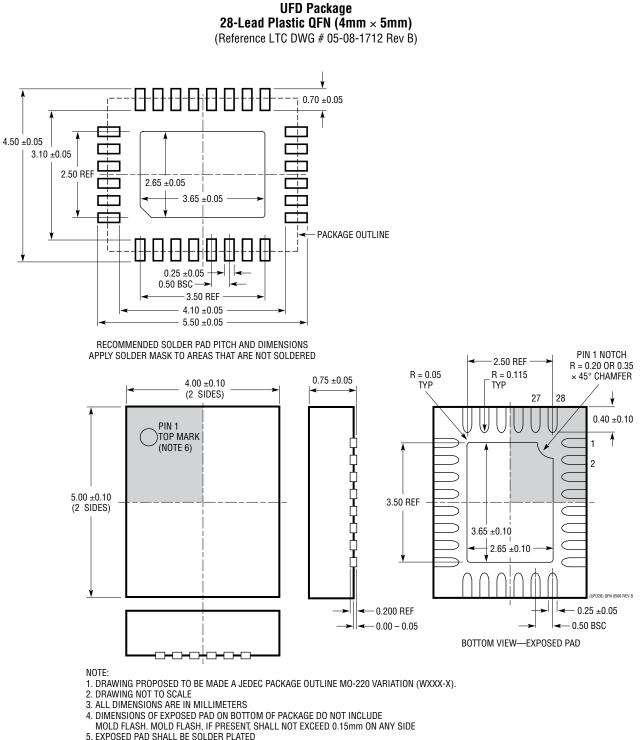

- 20-Lead TSSOP and 28-Lead QFN Packages

### **APPLICATIONS**

- Dual Rail Power for Signal Chain.

- Buck/Buck, Buck/Boost, Boost/Boost, Boost/Invert, Invert/Invert, Buck/Invert

### DESCRIPTION

LT8471EFE is a dual PWM DC/DC converter containing two internal 2A, 50V switches and an additional 500mA switch to facilitate step-down and inverting conversion. Each 2A channel can be independently configured as a buck, boost, SEPIC, flyback or inverting converter. Capable of generating positive and negative outputs from a single input rail, the LT8471 is ideal for many local power supply designs.

The LT8471 has an adjustable oscillator, set by a resistor placed from the RT pin to ground. Additionally, the LT8471 can be synchronized to an external clock. The free running or synchronized switching frequency range of the part can be set between 100kHz and 2MHz.

Additional features such as frequency foldback, soft-start, and power good are integrated. The LT8471 is available in 20-lead TSSOP and 28-Lead ( $4mm \times 5mm$ ) QFN packages.

𝗭, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

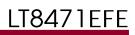

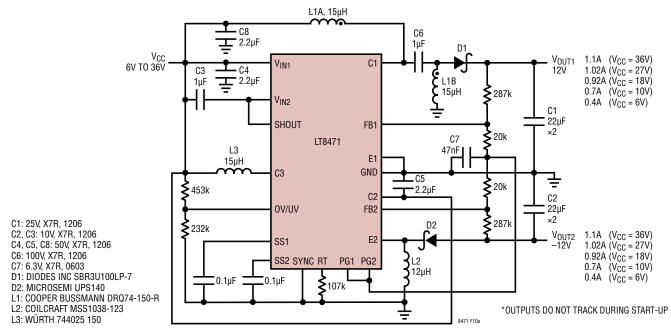

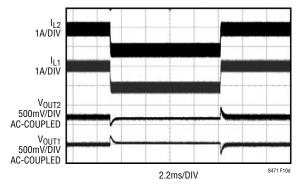

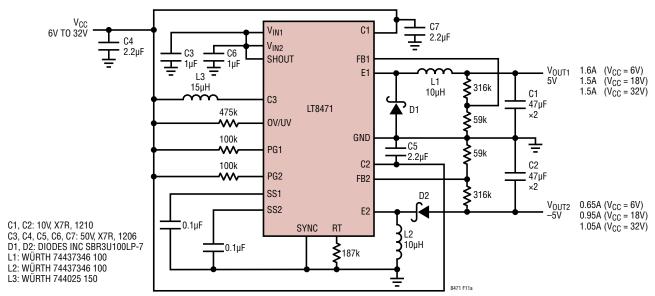

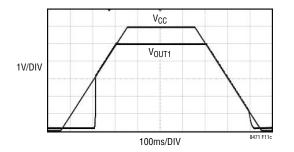

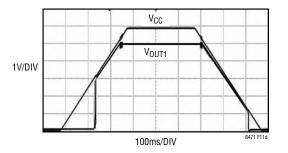

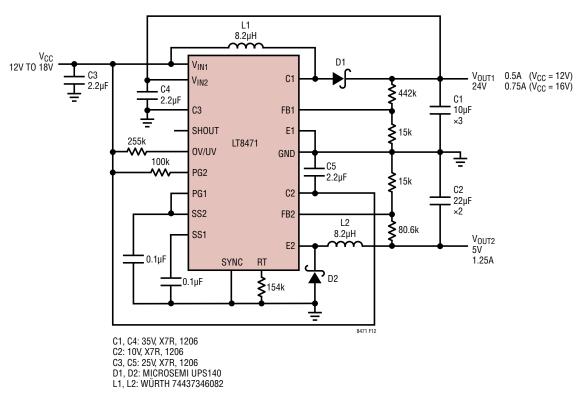

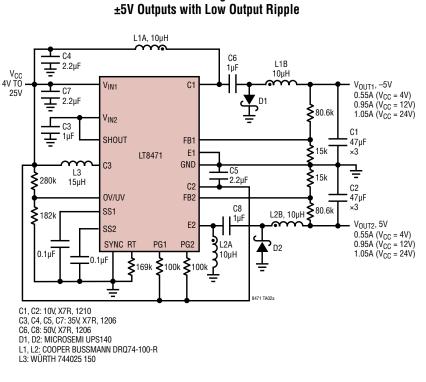

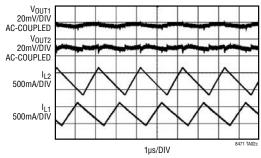

### TYPICAL APPLICATION

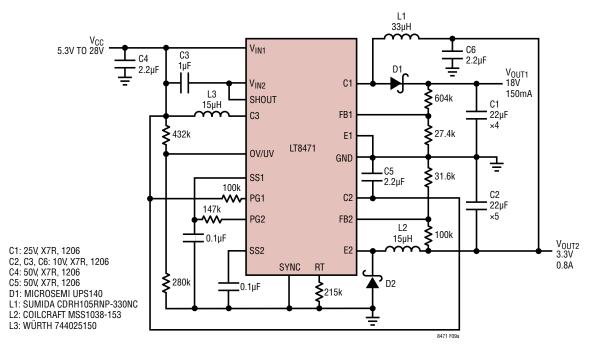

6V to 32V to  $\pm$ 5V, Dual DC/DC Converter

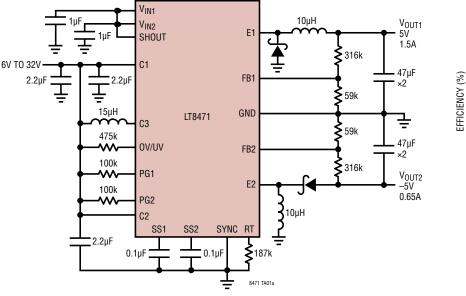

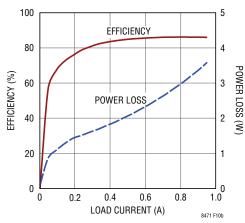

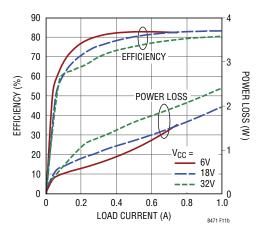

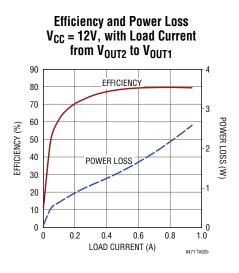

# Efficiency and Power Loss Load from $V_{OUT1}$ to $V_{OUT2}$

**LINEAR** TECHNOLOGY

### **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                                 |              |

|----------------------------------------------------------|--------------|

| V <sub>IN1</sub> , V <sub>IN2</sub> Voltages             | 0.3V to 50V  |

| C1, C2 Voltages                                          | –0.4V to 50V |

| E1, E2 Voltages                                          |              |

| $V_{C1}$ to $V_{E1}$ and $V_{C2}$ to $V_{E2}$ Voltages   | 0.4V to 60V  |

| $V_{IN1}$ to $V_{E1}$ and $V_{IN2}$ to $V_{E2}$ Voltages |              |

| Low Side Configurations (Note 6)                         | 0.4V to 40V  |

| High Side Configurations (Note 6)                        | 0.4V to 60V  |

| $V_{IN1}$ to $V_{C1}$ and $V_{IN2}$ to $V_{C2}$ Voltages |              |

| High Side Configurations (Note 6)                        | 0.4V to 40V  |

| C3 Voltage                                               | –0.4V to 50V |

| RT Voltage                                               | 0.3V to 5V   |

| SYNC Voltage                                             | 0.3V to 5.5V |

|                                                          |              |

| SS1, SS2                             | –0.3V to 2.5V  |

|--------------------------------------|----------------|

| FB1, FB2 Voltages                    | –2.5V to 2.5V  |

| PG1, PG2 Voltages                    | 0.3V to 50V    |

| OV/UV Voltage                        | 0.3V to 5V     |

| SHOUT Voltage                        | 0.3V to 50V    |

| Operating Junction Temperature Range | ;              |

| LT8471E (Notes 2, 5)                 | –40°C to 125°C |

| LT8471I (Notes 2, 5)                 | –40°C to 125°C |

| LT8471H (Notes 2, 5)                 | –40°C to 150°C |

| Storage Temperature Range            | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |                |

| FE Package                           | 300°C          |

### PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|------------------|---------------|---------------------------------|-------------------|

| LT8471EFE#PBF    | LT8471EFE#TRPBF  | LT8471FE      | 20-Lead Plastic TSSOP           | -40°C to 125°C    |

| LT8471IFE#PBF    | LT8471IFE#TRPBF  | LT8471FE      | 20-Lead Plastic TSSOP           | -40°C to 125°C    |

| LT8471HFE#PBF    | LT8471HFE#TRPBF  | LT8471FE      | 20-Lead Plastic TSSOP           | -40°C to 150°C    |

| LT8471EUFD#PBF   | LT8471EUFD#TRPBF | 8471          | 28-LEAD (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LT8471IUFD#PBF   | LT8471IUFD#TRPBF | 8471          | 28-LEAD (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN1</sub> = V<sub>IN2</sub> = 5V, unless otherwise noted (Note 2).

| PARAMETER                                                            | CONDITIONS                                                                                    |   | MIN          | ТҮР          | MAX          | UNITS      |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---|--------------|--------------|--------------|------------|

| Input Voltage (V <sub>IN1</sub> , V <sub>IN2</sub> )                 |                                                                                               | ٠ | 2.6          |              | 50           | V          |

| Quiescent Current (V <sub>IN1</sub> , Skyhook Disabled)              | V <sub>OV/UV</sub> = 1.3V, Not Switching                                                      |   |              | 2.2          | 3.3          | mA         |

| Quiescent Current (V <sub>IN1</sub> , Skyhook Enabled)               | $V_{OV/UV} = 1.3V, C3 = 5V, Not Switching$                                                    |   |              | 2.4          | 4            | mA         |

| Quiescent Current (V <sub>IN2</sub> )                                | V <sub>OV/UV</sub> = 1.3V, Not Switching                                                      |   |              | 29           | 42           | μA         |

| Quiescent Current in Shutdown (V <sub>IN1</sub> + V <sub>IN2</sub> ) | $V_{OV/UV} = 0V$                                                                              |   |              | 0.01         | 1            | μA         |

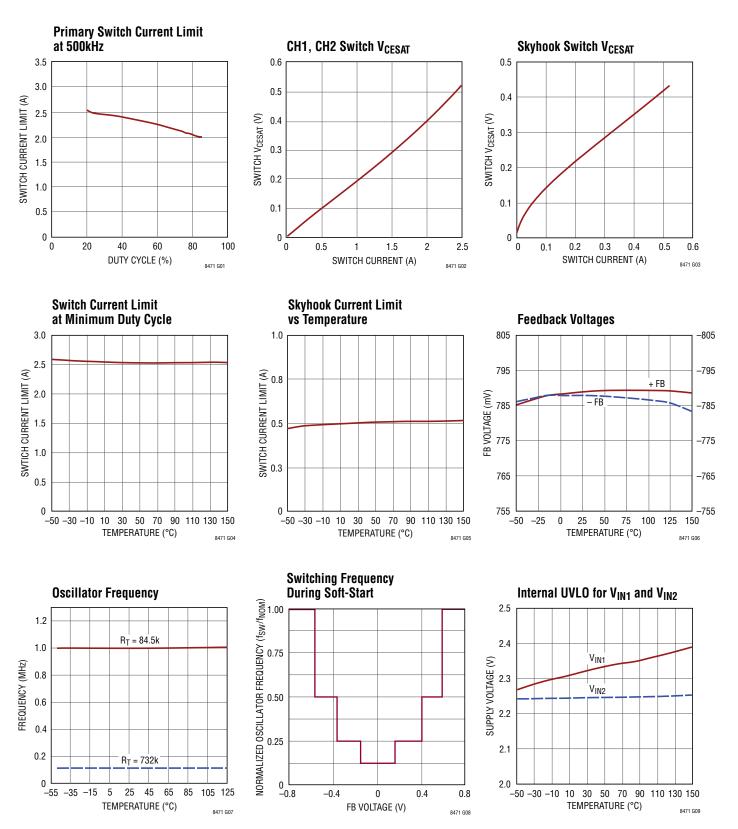

| Positive Feedback Voltage (FB1, FB2)                                 |                                                                                               | ٠ | 773          | 789          | 805          | mV         |

| Negative Feedback Voltage<br>(FB1, FB2)                              | (LT8471E,I)<br>(LT8471H)                                                                      | • | -806<br>-806 | -788<br>-788 | -770<br>-767 | mV<br>mV   |

| Feedback Pin Bias Current (FB1, FB2)                                 | $V_{FB}$ = Positive Feedback Voltage, Current Out of Pin $V_{FB}$ = Negative Feedback Voltage |   | -100         | 30<br>0      | 200<br>100   | nA<br>nA   |

| Error Amp Transconductances                                          | Primary Channels, $\Delta I = 2\mu A$                                                         |   |              | 70           |              | µmhos      |

| Error Amp Voltage Gains                                              | Primary Channels                                                                              |   |              | 95           |              | V/V        |

| Reference Line Regulation                                            | $2.6V \le V_{IN1} \le 50V$                                                                    |   |              | 0.008        | 0.05         | %/V        |

| Switching Frequency, f <sub>OSC</sub>                                | $\begin{array}{l} R_{T} = 46.4k \\ R_{T} = 732k \end{array}$                                  | • | 1.55<br>100  | 1.8<br>117   | 2.05<br>135  | MHz<br>kHz |

| Switching Frequency in Foldback                                      | All Channels. Compared to Normal f <sub>OSC</sub>                                             |   |              | 1/8          |              | Ratio      |

| Switching Frequency Range                                            | Synchronizing                                                                                 | ٠ | 100          |              | 2000         | kHz        |

| SYNC High Level for Sync                                             |                                                                                               | ٠ | 1.3          |              |              | V          |

| SYNC Low Level for Sync                                              |                                                                                               | ٠ |              |              | 0.4          | V          |

| SYNC Clock Pulse Duty Cycle                                          | V <sub>SYNC</sub> = 0V to 2V                                                                  |   | 35           |              | 65           | %          |

| Recommended Minimum SYNC Ratio $f_{SYNC}/f_{OSC}$                    |                                                                                               |   |              | 3⁄4          |              | Ratio      |

| Switching Phase Between Primary Channels                             | R <sub>T</sub> = 46.4k<br>R <sub>T</sub> = 732k                                               |   | 170<br>170   |              | 200<br>200   | Deg<br>Deg |

| Skyhook Boost Voltage                                                | V <sub>SHOUT</sub> – V <sub>C2</sub> , Skyhook Enabled                                        |   | 3.0          | 4.25         | 5.4          | V          |

| Minimum Switch Off-Time                                              | Primary Channels (Note 7)<br>Skyhook Channel (Note 7)                                         |   |              | 170<br>100   |              | ns<br>ns   |

| Minimum Switch On-Time                                               | Primary Channels(Note 7)<br>Skyhook Channel (Note 7)                                          |   |              | 220<br>30    |              | ns<br>ns   |

### **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{IN1} = V_{IN2} = 5V$ , unless otherwise noted (Note 2).

| PARAMETER                                                    | CONDITIONS                                                                                                                                     |   | MIN           | ТҮР           | MAX           | UNITS    |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------|---------------|---------------|----------|

| Switch Current Limit (Primary Channels)                      | Minimum Duty Cycle (Note 3)<br>Maximum Duty Cycle (Notes 3, 4)                                                                                 | • | 2.1<br>1.35   | 2.55<br>1.8   | 3.2<br>2.5    | A<br>A   |

| Switch Current Limit (Skyhook)                               | (Note 3)                                                                                                                                       | • | 400           | 500           | 600           | mA       |

| Primary Switches V <sub>CESAT</sub>                          | I <sub>C1</sub> or I <sub>C2</sub> = 1.5A                                                                                                      |   |               | 300           |               | mV       |

| Skyhook Switch V <sub>CESAT</sub>                            | I <sub>C3</sub> = 250mA                                                                                                                        |   |               | 250           |               | mV       |

| C1, C2 Leakage Current                                       | $\label{eq:Vc1} \begin{array}{l} V_{C1} = V_{C2} = 12V, \ V_{E1} = V_{E2} = 0V, \ V_{0V/UV} = 0V, \\ Current \ into \ Pin \end{array}$         |   |               | 0.01          | 1             | μA       |

| C3 Leakage Current                                           | $V_{C3} = 12V, V_{OV/UV} = 0V$                                                                                                                 |   |               | 0.01          | 1             | μA       |

| E1, E2 Leakage Current                                       | $V_{0V/UV} = 0V$ , Current Out of Pin<br>$V_{C1} = V_{C2} = 20V$ , $V_{E1} = V_{E2} = 5V$<br>$V_{C1} = V_{C2} = 5V$ , $V_{E1} = V_{E2} = -10V$ |   |               | 0.01<br>0.01  | 1             | μΑ<br>μΑ |

| Schottky Reverse Leakage                                     | V <sub>REVERSE</sub> = 12V<br>V <sub>REVERSE</sub> = 50V                                                                                       |   |               | 0.01<br>0.02  | 1<br>2        | μΑ<br>μΑ |

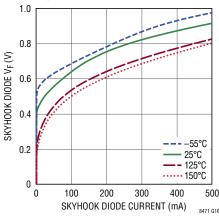

| Schottky Forward Voltage                                     | I <sub>DIODE</sub> = 100mA                                                                                                                     |   |               | 650           |               | mV       |

| Start-Up Characteristics                                     |                                                                                                                                                |   |               |               |               |          |

| Soft-Start Charge Current                                    | V <sub>SS1</sub> , V <sub>SS2</sub> = 50mV, Current Flows Out of SS1, SS2 Pins                                                                 | • | 5.5           | 8.5           | 11.5          | μA       |

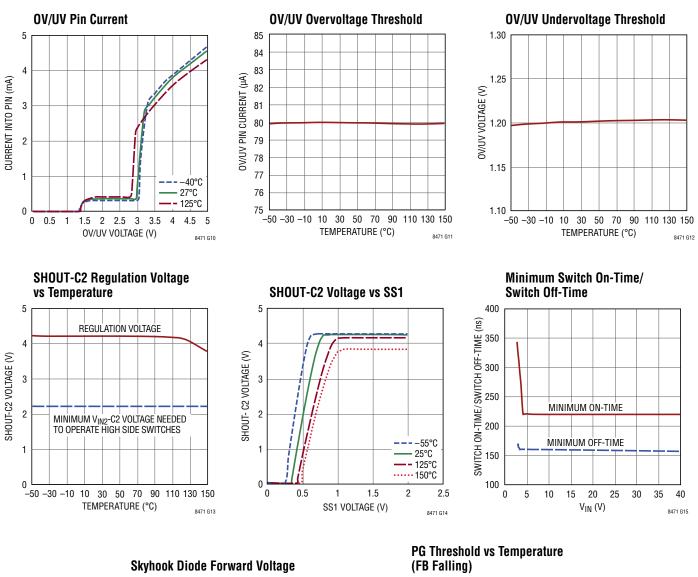

| OV/UV Current for OVLO                                       | Current into OV/UV Pin. V <sub>OV/UV</sub> Internally Clamped to 1.37V, Current Rising                                                         | • | 76            | 80            | 84            | μA       |

| OV/UV Pin Bias Current                                       | V <sub>OV/UV</sub> =1V                                                                                                                         |   |               | 0.01          | 0.5           | μA       |

| OV/UV Minimum Input Voltage High                             | Active Mode, OV/UV Rising<br>Active Mode, OV/UV Falling                                                                                        | • | 1.165<br>1.13 | 1.215<br>1.18 | 1.265<br>1.22 | V<br>V   |

| OV/UV Input Voltage Low                                      | Shutdown Mode                                                                                                                                  | • |               |               | 0.3           | V        |

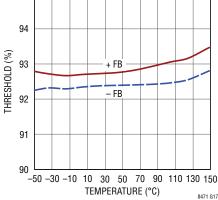

| FB Pin Threshold for Power Good<br>(Positive Output Voltage) | FB Rising<br>FB Falling                                                                                                                        | • | 715<br>708    | 740<br>730    | 765<br>752    | mV<br>mV |

| FB Pin Threshold for Power Good<br>(Negative Output Voltage) | FB Falling<br>FB Rising                                                                                                                        | • | -766<br>-755  | -736<br>-727  | -706<br>-699  | mV<br>mV |

| PG1, PG2 Voltage Output Low                                  | $V_{FB} = 0.6V, I_{PG} = 250\mu A$                                                                                                             |   |               | 0.32          | 0.6           | V        |

| PG1, PG2 Leakage                                             | V <sub>PG1</sub> , V <sub>PG2</sub> = 12V, PG Driver Off                                                                                       |   |               | 0.01          | 1             | μA       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LT8471E is guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LT8471I is guaranteed over the full -40°C to 125°C. The LT8471H is guaranteed over the full -40°C to 150°C operating junction temperature range. Operating lifetime is derated at junction temperatures greater than 125°C.

**Note 3:** Current limit guaranteed by design and/or correlation to static test. **Note 4:** Current Limit measured at equivalent switching frequency of 1MHz.

**Note 5:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 6:** Low side and high side configurations are discussed in the Switch Configurations and the Skyhook Regulator section.

Note 7: Minimum switch on-time, off-time is guaranteed by design.

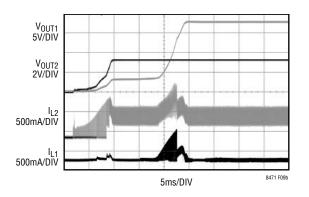

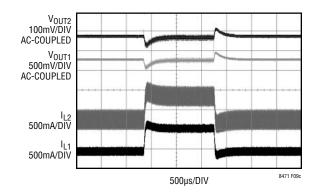

### TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise specified.

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise specified.

### PIN FUNCTIONS

**C1, C2 (Pins 1, 20):** Collector Pins. These are the collectors of the primary internal NPN power switches. If either pin is tied to a DC voltage, it must be locally bypassed; if either pin is a switching pin, minimize trace area connected to the pin to minimize EMI. When the Skyhook channel is used, the C2 pin must be tied to the input voltage of the Skyhook channel.

**C3 (Pin 13):** Skyhook Collector Pin. This is the collector of the internal NPN power switch for the Skyhook channel. If the Skyhook channel is used, minimize the metal trace area connected to this pin to minimize EMI. If the Skyhook channel is not used, tie the C3 pin to GND.

**E1, E2 (Pins 2, 19):** Emitter Pins. These are the emitters of the primary internal NPN power switches. Unless grounded, minimize trace area connected to these pins to minimize EMI.

**FB1, FB2 (Pins 5, 16):** Feedback Pins for Primary Channels. Connect a resistor divider between  $V_{OUT}$ , FB and GND to set the output voltage.

**GND (Pins 10, 11,12, Exposed Pad 21):** Ground. All of the ground pins must be soldered directly to the local ground plane. The exposed pad metal of the package provides both electrical contact to ground and good thermal contact to the printed circuit board.

**OV/UV (Pin 6)**: Overvoltage/Undervoltage Pin. Tie to 1.215V (typical) or more to enable the device; ground to shut down. Configurable as a UVLO and OVLO by connecting to an external resistor divider. See the Applications Information section for more information.

**PG1, PG2 (Pins 4, 17):** Power Good Pins. Connect pull-up resistors to these pins. These open-drain output pins are

pulled low when their respective output voltages are more than 7.5% below their target output voltages (as set by the external feedback resistors). When the output voltage is above 92.5% of the target voltage, the respective PG pin driver turns off, allowing the PG voltage to rise and indicate that the regulated output voltage is good.

**RT (Pin 7):** Timing Resistor Pin. Adjusts the switching frequency. Place a resistor from this pin to ground to set the frequency to a fixed free-running level. Do not float this pin.

**SHOUT (Pin 14):** Skyhook Output Voltage Pin. This is the cathode of the internal Schottky diode and the output of the Skyhook boost converter.

**SS1, SS2 (Pins 8, 15):** Soft Start Pins. Place a soft-start capacitor on each pin. Upon start-up, the SS pins will be charged by (nominally) 250k resistors to about 2.15V.

**SYNC (Pin 9):** To synchronize the switching frequency to an outside clock, simply drive this pin with a clock. The high voltage level of the clock needs to exceed 1.3V, and the low level should be less than 0.4V. Drive this pin to less than 0.4V to revert to the internal free running clock. See the Applications Information section for more information.

$V_{IN1}$  (Pin 3): Input Supply Pin 1. This is the power supply pin for primary channel 1 and the Skyhook channel. This pin also provides power to additional circuitry common to all channels.  $V_{IN1}$  must be greater than 2.6V for any channel to operate.  $V_{IN1}$  must be locally bypassed.

$V_{IN2}$  (Pin 18): Input Supply Pin 2. This is the power supply pin for primary channel 2 and must be greater than 2.6V when channel 2 is in use.  $V_{IN2}$  must be locally bypassed.

# <u>LT8471EFE</u>

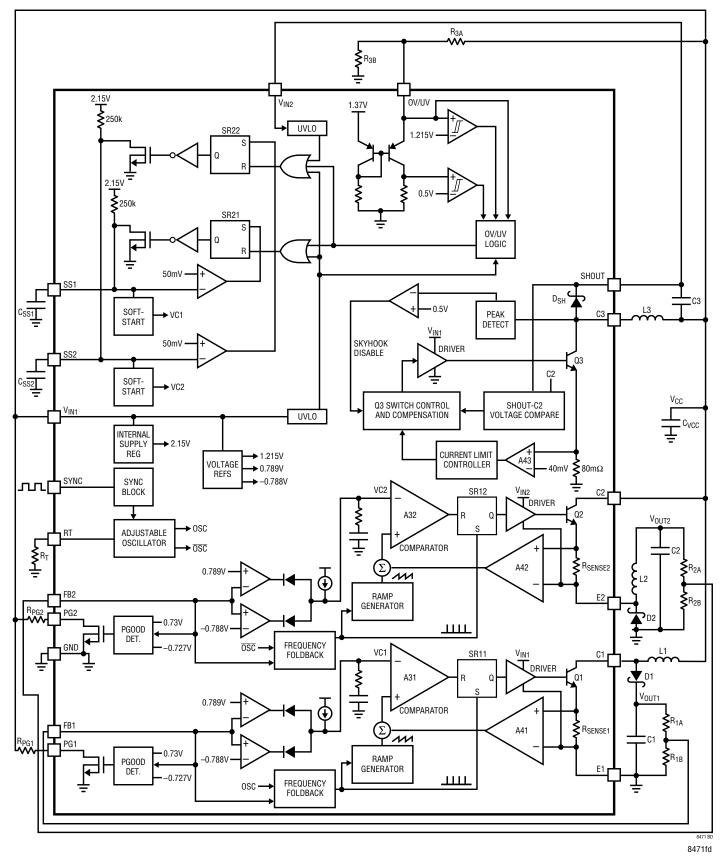

# **BLOCK DIAGRAM**

8

### OPERATION

The LT8471 consists of two primary channels, each with a 2A power switch. One Skyhook channel is also available with a 500mA power switch to support the primary channels when performing step-down conversions. The maximum voltage between V<sub>IN1</sub> and E1 (or V<sub>IN2</sub> and E2) is 40V when E1 (or E2) is grounded. This is the case for boost, SEPIC, flyback and dual-inductor inverting topologies. The maximum allowed voltage between V<sub>IN1</sub> and E1 (or V<sub>IN2</sub> and E2) is 60V when E1 (or E2) is allowed to toggle, such as in buck, ZETA and single-inductor inverting topologies.

#### **Primary Channels**

The two primary channels, 1 and 2, can be independently configured as boost, buck, SEPIC, ZETA, flyback or inverting DC/DC converters to adapt into various applications. Both channels use a constant-frequency, current mode control scheme to provide line and load regulation (refer to the Block Diagram). The channel 1 clock is in phase with the internal oscillator or the SYNC pin if it is toggling. In order to reduce transient switching spikes, the clock for channel 2 is approximately 180° out-of-phase with the channel 1 clock.

At the start of each clock phase, an SR latch (SR11/SR12 in the Block Diagram) is set, turning on the internal power switch (Q1/Q2 in the Block Diagram) for the respective channel. An amplifier (A41/A42 in the Block Diagram) and a comparator (A31/A32 in the Block Diagram) monitor the current flowing through the internal power switch, turning the switch off when the current reaches a level determined by the voltage at VC1/VC2. An error amplifier measures the output voltage through an external resistor divider tied to the FB1/FB2 pin and servos the VC1/VC2 voltage. If the error amplifier's output (VC1/VC2) increases, more current is delivered to the output; if it decreases, less current is delivered. An internal clamp on the VC1/VC2 voltage provides current limit.

Both of the primary channels contain a power good comparator which trips when the corresponding FB pin voltage is at 92.5% of its regulated value. The PG1 and PG2 outputs are driven by open-drain N-channel MOSFET devices that are off when the respective output is in regulation, allowing external resistors to pull the PG1/PG2 pins high. The PG1 and PG2 pin states are only valid when the respective channel is enabled and  $V_{\text{IN1}}$  is above 2.6V.

#### Skyhook Channel

When either channel is configured as a buck, ZETA or single-inductor inverting converter, the respective  $V_{IN}$  pin(s) must be boosted above the input voltage,  $V_{CC}$ . The boosted supply provides base current to the appropriate Q1 and/or Q2 NPN power switch. The Skyhook channel provides this boosted voltage to the SHOUT pin which must also be connected to  $V_{IN2}$  and/or  $V_{IN1}$  as needed.

The Skyhook is a constant-frequency, voltage mode boost converter including a Schottky diode integrated on chip. The Skyhook output, SHOUT, is regulated to a fixed voltage (4.25V typical) above the C2 pin which must be connected to a DC voltage (typically  $V_{CC}$ ). If the Skyhook is not needed it can be disabled by tying the C3 pin to GND. This also reduces the current draw from  $V_{IN1}$ . Refer to the Applications Information section for more information about the proper use of the Skyhook channel.

The Skyhook operates as follows: An error amplifier measures the output voltage (SHOUT) through the SHOUT-C2 voltage comparator and servos an internal control voltage. The control voltage determines the on-time of the Q3 power switch for each cycle, and thus, the amount of current being delivered to SHOUT. Loop compensation is integrated in the chip. Comparator A43 monitors the current in the power switch Q3 in order to detect over current conditions. If current in excess of 500mA (typ) is detected, switch Q3 is immediately turned off.

#### **Start-Up Operation**

Several functions are provided to enable a clean start-up for the LT8471.

- First, the OV/UV pin voltage is monitored by an internal voltage reference to give a precise turn-on voltage range. An external resistor (or resistor divider) can be connected from the input power supply to the OV/UV pin to provide a user-programmable undervoltage and overvoltage lockout function.

- Second, the soft-start circuitry provides for a gradual ramp-up of the switch current for the primary channels

# OPERATION

and a gradual ramp-up of duty cycle for the Skyhook channel. When the part is brought out of shutdown, the external SS capacitors are first discharged (providing protection against OV/UV pin glitches and slow ramping). Next, internal 250k resistors pull the SS pins up to ~2.15V. By connecting an external capacitor to each of the SS pins, the voltage ramp rates on the pins can be set. Typical values for the soft-start capacitor range from 100nF to 1 $\mu$ F.

Finally, the primary channels' switching frequency is folded back by 2, 4, or 8 times when the corresponding FB pin voltage is below certain thresholds (see the Typical Performance Characteristics section). This feature reduces the minimum duty cycle that the part can achieve, thus allowing better control of the switch current during start-up. The slope compensation function is disabled during foldback to increase the available current that can be delivered to the output.

#### Thermal Shutdown Operation

Not shown in the Block Diagram is the thermal shutdown circuit. If the temperature of the part exceeds approximately 164°C, the SR21 and SR22 latches are set. A full soft-start cycle will then be initiated after the temperature drops below approximately 162.5°C. The thermal shutdown circuit protects the power switches as well as the external components connected to the LT8471.

### **APPLICATIONS INFORMATION**

#### **Input Supply Requirements**

$V_{\rm IN1}$  is the main power supply of the LT8471. It powers channel 1, the Skyhook channel and most of the internal control and bias circuits for both channels. It must be powered up to enable any channel of the LT8471.  $V_{\rm IN2}$  is the power supply for channel 2, and only needs to be powered up when channel 2 is used. When  $V_{\rm IN2}$  is not powered up, channel 2 will shut down.

#### Switch Configurations and the Skyhook Regulator

The primary channel NPN power switches can be connected in low side or high side configurations. A low side connection is when the power switch is on the lower voltage side of the inductor while the switch is on. The boost, SEPIC, flyback and dual-inductor inverting configurations use low side power switches. Conversely, a high side connection is when the power switch is on the higher voltage side of the inductor when it is on. The buck, ZETA and single-inductor inverting configurations use high side power switches. Channels 1 and 2 can be configured for high side or low side switching and do not need to be configured in the same way as the other. In the low side configurations, the E pin is typically tied to ground and the respective C pin toggles.  $V_{IN}$  for the respective channel must operate in a range of 2.6V to 40V.

High side configurations require that the C pin be tied to a positive DC voltage supply and the respective E pin toggles. The channel's  $V_{IN}$  pin should be at least 2.2V (typical) higher than the respective C pin to provide adequate drive to the base of the NPN power switch. When configured with a high side switch, the channel's  $V_{IN}$  can operate up to 50V above ground, 60V above the respective E pin voltage, and 40V above the respective C pin voltage.

The Skyhook boost regulator is available to provide additional V<sub>IN</sub> voltage when it is needed to support high side switch topologies. When enabled, the Skyhook output voltage (SHOUT) is regulated to 4.25V (typical) above the C2 pin voltage. Figure 1 shows an example where the application input voltage is 6V to 32V. The Skyhook boost converter regulates SHOUT, V<sub>IN1</sub> and V<sub>IN2</sub> to 10.25V to 36.25V insuring that the V<sub>IN1</sub> and V<sub>IN2</sub> pins are typically 4.25V above the C1 and C2 pins. More information about the Skyhook regulator is available in later sections.

#### Internal Undervoltage Lockouts

The LT8471 monitors  $V_{IN1}$  and  $V_{IN2}$  supply voltages in case either drops below a minimum operating level (typically about 2.35V and 2.25V, respectively).

When  $V_{IN1}$  is detected low, all power switches are deactivated, and while sufficient  $V_{IN1}$  voltage persists, the soft-start capacitors for both SS1 and SS2 are discharged. After  $V_{IN1}$  is detected high, the channel 1 power switch is re-enabled and SS1 begins charging.

When  $V_{IN2}$  is detected low, the channel 2 power switch is deactivated, and while sufficient  $V_{IN1}$  voltage persists, the soft-start capacitor for SS2 is discharged. After both  $V_{IN1}$  and  $V_{IN2}$  are detected high, the channel 2 power switch is re-enabled and SS2 begins charging.

#### Oscillator

The internal free-running oscillator can set the operating frequency of the LT8471. When the SYNC pin is driven low (< 0.4V), the frequency of operation is set by a resistor from RT to ground. An internally trimmed timing capacitor resides inside the IC. The oscillator frequency is calculated using the following formula:

$$f_{OSC} = \frac{85.5}{R_T + 1}$$

where  $f_{OSC}$  is in MHz and  $R_T$  is in  $k\Omega$ . Conversely,  $R_T$  (in  $k\Omega$ ) can be calculated from the desired frequency (in MHz) using:

$$R_{\rm T} = \frac{85.5}{f_{\rm OSC}} - 1$$

#### **Clock Synchronization**

The operating frequency of the LT8471 can be synchronized to an external clock source. To synchronize to the external source, simply provide a digital clock signal into the SYNC pin. The LT8471 will operate at the SYNC clock frequency. The LT8471 will revert to the internal freerunning oscillator clock after SYNC is driven low for a few free-running clock cycles. Driving SYNC high for an extended period of time effectively stops the operating clock and prevents latches SR11 and SR12 from becoming set (see the Block Diagram). As a result, the switching operation of the LT8471 stops, and all the power switches are turned off.

The duty cycle of the SYNC signal must be between 35% and 65% for proper operation. Also, the frequency of the SYNC signal must meet the following two criteria:

- 1. SYNC may not toggle outside the frequency range of 100kHz to 2MHz unless it is set low to enable the free-running oscillator.

- 2. The SYNC frequency can always be higher than the free-running oscillator frequency,  $f_{OSC}$ , but should not be less than 25% below  $f_{OSC}$ .

#### **Operating Frequency Selection**

There are several considerations in selecting the operating frequency of the converter. The first is staying clear of sensitive frequency bands, which cannot tolerate any spectral noise. For example, in products incorporating RF communications, the 455kHz IF frequency is sensitive to any noise, therefore switching above 600kHz is desired. Some communications have sensitivity to 1.1MHz, and in that case, a 1.5MHz switching converter frequency may be employed. The second consideration is the physical size of the converter. As the operating frequency goes up, the inductor and filter capacitors go down in value and size. The trade-off is efficiency, since the switching losses due to NPN base charge (see the Power and Thermal Calculation section), Schottky diode charge, and other capacitive loss terms increase proportionally with frequency.

#### Soft-Start

The LT8471 contains soft-start circuitry to limit peak switch currents during start-up. High start-up current is inherent in switching regulators since the feedback loop is saturated due to  $V_{OUT}$  being far from its final value. The regulator tries to charge the output capacitor as quickly as possible, which results in large peak currents.

The start-up current can be limited by connecting external capacitors (typically 100nF to  $1\mu$ F) to the SS1 and SS2 pins. The capacitors are slowly charged to ~2.15V by internal

250k resistors after the part is activated. SS1 pin voltages below ~0.8V reduce the duty cycle of the Skyhook channel, and below ~1.4V reduce the current limit of channel 1. SS2 voltages below ~1.4V reduce the current limit of channel 2. Thus, the gradual ramping of the SS voltages also gradually increases the current limits of the primary channels and the duty cycle of the Skyhook channel. This, in turn, allows the output capacitors for each channel to charge gradually toward its final value while limiting the start-up currents.

In the event of a shutdown (OV/UV pin), internal undervoltage lockout (UVLO) or a thermal lockout, the soft-start capacitors are automatically discharged to <50mV before charging resumes, assuring that the soft-starting occurs after every reactivation of the chip.

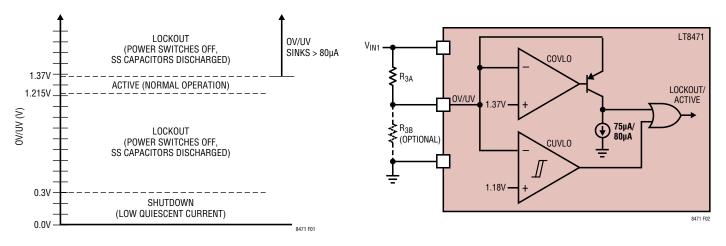

#### Shutdown

The OV/UV pin is used to enable and disable the chip. When configured properly, the OV/UV pin can serve as both an undervoltage and an overvoltage detector as discussed further in the next section. When the OV/UV voltage is below 1.215V (typ) switching activity is disabled as shown in Figure 1 (lockout state). When OV/UV is below 300mV,

Figure 1. Chip States vs OV/UV Voltage

quiescent current becomes very low and the part is completely in shutdown. Voltages between 1.215V and 1.37V enable the part (ACTIVE state) for normal operation. The OV/UV pin is internally clamped to approximately 1.37V and should always be connected through a resistor to limit the current. If the OV/UV pin current exceeds 80µA (typ), switching is disabled and the part enters the lockout state. See the OV/UV pin current graph in the Typical Performance Characteristics section.

When in the lockout state, the power switches are disabled and the SR21 and SR22 latches are set. This causes the soft-start capacitors to discharge until active operation is enabled. Although the power switches are disabled, the lockout state does not necessarily reduce quiescent current until the OV/UV voltage is near or below the shutdown threshold.

Due to the 1.37V clamping circuit, OV/UV should always be connected through a resistor to limit the current. If the over and undervoltage functions are not used, the OV/UV pin can be driven digitally through a current limiting resistor.

Figure 2 shows how to configure an overvoltage lockout (OVLO) and/or undervoltage lockout (UVLO) for the

Figure 2. Configurable OVLO and UVLO

LT8471. Comparator CUVLO detects undervoltage conditions by comparing the OV/UV pin to typical thresholds of 1.215V (rising) and 1.18V (falling). The COVLO comparator detects over voltage conditions by comparing the OV/UV pin current to typical thresholds of  $80\mu$ A (rising) and  $75\mu$ A (falling).

Possible reasons to use the UVLO and/or OVLO functions are as follows: A switching regulator draws constant power from the source, so source current increases as source voltage drops. This looks like a negative resistance load to the source and can cause the source to current-limit or latch up under low source voltage conditions. UVLO prevents the regulator from operating at source voltages where these problems might occur. The OVLO function is used to stop the switching regulator(s) in cases where the input supply voltage overshoots higher than desired.

As an example,  $V_{IN1}$  overvoltage and undervoltage thresholds can be set independently by properly choosing  $R_{3A}$  and  $R_{3B}$ . Use the following formulas to determine the resistor values:

$$R_{3A} = \left(\frac{V_{0VL0}^{+}}{80\mu A}\right) - \left(\frac{1.37 \cdot V_{UVL0}^{-}}{1.18 \cdot 80\mu A}\right)$$

$$R_{3B} = \left(\frac{1.18}{V_{UVL0}^{-} - 1.18}\right) \cdot R_{3A}$$

where:

$V_{OVLO^+}$  is the desired rising OVLO threshold  $V_{UVLO^-}$  is the desired falling UVLO threshold

After  $R_{3A}$  and  $R_{3B}$  have been selected, the UVLO and OVLO rising and falling thresholds can be determined using:

$$V_{0VL0}^{+} = 1.37 \cdot \left(\frac{R_{3A} + R_{3B}}{R_{3B}}\right) + 80\mu A \cdot R_{3A}$$

$$V_{0VL0}^{-} = 1.37 \cdot \left(\frac{R_{3A} + R_{3B}}{R_{3B}}\right) + 75\mu A \cdot R_{3A}$$

$$V_{UVL0}^{+} = 1.215 \cdot \left(\frac{R_{3A} + R_{3B}}{R_{3B}}\right)$$

$$V_{UVL0}^{-} = 1.18 \cdot \left(\frac{R_{3A} + R_{3B}}{R_{3B}}\right)$$

where:

$V_{OVLO^+}$  and  $V_{OVLO^-}$  are the rising and falling OVLO thresholds, respectively.

$V_{UVLO^+}$  and  $V_{UVLO^-}$  are the rising and falling UVLO thresholds, respectively.

There are a few limitations in selecting the OVLO and UVLO threshold voltages.

1. The UVLO threshold must be at least 2.6V so that it's higher than the minimum operating voltage the input supply. If the UVLO function is not needed,  $R_{3B}$  can be omitted and  $R_{3A}$  can be calculated using:

$$R_{3A} = \left(\frac{V_{0VL0}^{+} - 1.37V}{80\mu A}\right)$$

2. The following relationship must be satisfied:

$$\frac{V_{0VL0}^{}}{V_{UVL0}^{}} > \frac{1.37}{1.18} = 1.161$$

As the ratio of  $V_{OVLO}$  to  $V_{UVLO}$  gets closer to 1.161, the required resistances for  $R_{3A}$  and  $R_{3B}$  become smaller, thus increasing the operating current.

The following example shows how to select  $R_{3A}$  and  $R_{3B}$  to disable the LT8471 for  $V_{IN1}$  voltages below 5V and above 15V.

First, check that the ratio of the OVLO to the UVLO threshold is greater than 1.161. Here, the ratio is 15V/5V = 3V, which satisfies the second rule just mentioned.

Next, calculate:

$$R_{3A} = \frac{15V}{80\mu A} - \frac{1.37 \cdot 5V}{1.18 \cdot 80\mu A} = 114.9k$$

Choose  $R_{3\text{A}}$  to be a standard value resistance of 118k. Next, calculate:

$$\mathsf{R}_{3\mathsf{B}} = \left(\frac{1.18\mathsf{V}}{5\mathsf{V} - 1.18\mathsf{V}}\right) \bullet 118\mathsf{k} = 36.5\mathsf{k}$$

Choose  $R_{3B}$  to be a standard value resistance of 36.5k.

After selecting the standard value resistors for  ${\rm R}_{3A}$  and  ${\rm R}_{3B},$  calculate the final thresholds using the formulas previously provided.

$$V_{OVLO^{+}} = 1.37 \cdot \left(\frac{118k + 36.5k}{36.5k}\right) + 80\mu A \cdot 118k$$

$$= 15.24V$$

$$V_{OVLO^{-}} = 1.37 \cdot \left(\frac{118k + 36.5k}{36.5k}\right) + 75\mu A \cdot 118k$$

$$= 14.65V$$

$$V_{UVLO^{+}} = 1.215 \bullet \left(\frac{118k + 36.5k}{36.5k}\right) = 5.14V$$

$$V_{\rm UVLO} = 1.18 \cdot \left(\frac{110k + 30.5k}{36.5k}\right) = 4.99V$$

#### Setting the Output Voltage (Primary Channels)

The output voltage is programmed with a resistor divider between the output and the FB pin. Choose 1% or better resistors according to:

$$\mathsf{R}_{\mathsf{A}} = \mathsf{R}_{\mathsf{B}} \bullet \left( \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{FB}}} - 1 \right)$$

where  $V_{FB}$  is the feedback voltage (0.789V typical for positive  $V_{OUT}$  and -0.788V for negative  $V_{OUT}$ ). Reference designators are as shown in the Block Diagram.

For example, for  $V_{OUT}$  = 10V, choose  $R_{1B}$  = 10k, then choose:

$$R_{1A} = 10k \bullet \left(\frac{10V}{0.789V} - 1\right) \simeq 115k$$

#### Start-Up Sequencing

Connecting one primary channel's PG pin to the other channel's SS pin is an easy way to sequence the start-up order of the outputs. For example, in most applications, connecting PG1 to SS2 will make the channel 1 output come up before the channel 2 output during the start-up. Because the skyhook channel does soft-start with the SS1 pin (see more details in the Soft-Start section), the following guidelines need to be applied if both power-up sequencing and the skyhook channel are used:

- 1. Connect PG1 directly to SS2 to make channel 1's output come up first (see Figure 12).

- 2. Connect a 147k resistor between PG2 and SS1 to make channel 2's output come up first.

An example using a 147k resistor connected between PG2 and SS1 is shown in Figure 9a. In this application, channel 1 is configured as a boost converter, and channel 2 is configured as a buck converter. The buck converter has to start up first as its output is connected to the input of the boost converter.

#### Power Switch Duty Cycle (Primary Channels)

In order to maintain loop stability and deliver adequate current to the load, the internal power switches (Q1 and Q2 in the Block Diagram) cannot remain on for 100% of each clock cycle. The maximum allowable duty cycle is given by:

$$DC_{MAX} = \left(\frac{T_{P} - MIN_{(OFF)TIME}}{T_{P}}\right) \bullet 100\%$$

where  $T_P$  is the clock period and  $MIN_{(OFF)TIME}$  is typically 170ns (refer to the Electrical Characteristics section).

The application should be designed so that the steady state duty cycle does not exceed  $DC_{MAX}$ . Duty cycle equations for several common topologies are given below, where  $V_D$  is the diode forward voltage drop and  $V_{CESAT}$  is typically 300mV at 1.5A.

$$DC_{BOOST} \cong \frac{V_{OUT} - V_{CC} + V_D}{V_{OUT} + V_D - V_{CESAT}}$$

$$DC_{BUCK} \cong \frac{V_{OUT} + V_D}{V_{CC} + V_D - V_{CESAT}}$$

$$DC_{1L_INV} \cong \frac{|V_{OUT}| + V_D}{V_{CC} + V_D - V_{CESAT} + |V_{OUT}|}$$

$$DC_{2L_INV} \cong \frac{|V_{OUT}| + V_D}{V_{CC} + V_D - V_{CESAT} + |V_{OUT}|}$$

$$DC_{SEPIC} \cong \frac{V_D + V_{OUT}}{V_{CC} + V_{OUT} + V_D - V_{CESAT}}$$

$$DC_{ZETA} \cong \frac{V_D + V_{OUT}}{V_{CC} + V_{OUT} + V_D - V_{CESAT}}$$

where  $V_{CC}$  is the positive input voltage to the DC/DC converter. See the Typical Applications section for examples.

The LT8471 can be used in configurations where the duty cycle is higher than  $DC_{MAX}$ , but it must be operated in the discontinuous conduction mode so that the effective duty cycle is reduced.

#### Inductor Selection (Primary Channels)

General Guidelines: The high frequency operation of the LT8471 allows for the use of small surface mount inductors. For high efficiency, choose inductors with high frequency core material, such as ferrite, to reduce core losses. To improve efficiency, choose inductors with more volume for a given inductance. The inductor should have low DCR (copper wire resistance) to reduce I<sup>2</sup>R losses, and must be able to handle the peak inductor current without saturating. Note that in some applications, the current handling requirements of the inductor can be lower, such as in the SEPIC topology, where each inductor only carries a fraction of the total switch current. Molded chokes or chip inductors usually do not have enough core area to support peak inductor currents in the 2A to 3A range. To minimize radiated noise, use a toroidal or shielded inductor. Note that the inductance of shielded core types will drop more as current increases, and will saturate more easily. See Table 1 for a list of inductor manufacturers. Thorough lab evaluation is recommended to verify that the following guidelines properly suit the final application.

| Table 1. Inducto | or Manufacturers |

|------------------|------------------|

|                  |                  |

| VENDOR           | PART NUMBER                  | WEB                 |

|------------------|------------------------------|---------------------|

| Coilcraft        | MSS1038, MSS7341 and LPS4018 | www.coilcraft.com   |

| Coiltronics      | DR, LD and CD Series         | www.coiltronics.com |

| Sumida           | CDRH105R Series              | www.sumida.com      |

| Würth Elektronik | WE-LHMI and WE-TPC Series    | www.we-online.com   |

**Minimum Inductance:** Although there can be a tradeoff with efficiency, it is often desirable to minimize board space by choosing smaller inductors. When choosing an inductor, there are two conditions that limit the minimum inductance; (1) providing adequate load current, and (2) avoiding subharmonic oscillation. Choose an inductance that is high enough to meet both of these requirements.

Adequate Load Current: Small value inductors result in increased ripple currents and thus, due to the limited peak switch current, decrease the average current that can be provided to a load ( $I_{OUT}$ ). In order to provide adequate load current, L should be at least:

where:

L = L1||L2 for dual uncoupled inductor topologies.

L = L1 = L2 for dual-coupled inductor topologies.

DC = Switch duty cycle in steady state.

$I_{LIM}$  = Switch current limit, typically about 2.3A at 50% duty cycle (see the Typical Performance Characteristics section).

$\eta$  = Power conversion efficiency (typically 88% for boost, 75% for dual inductor, 85% for buck and 80% for 1L inverting topologies at high currents).

$V_{CC}$  = Positive input voltage to the DC/DC converter. See the Typical Applications section for examples.

f = Switching frequency.

Negative values of L indicate that the output load current  $I_{OUT}$  exceeds the switch current limit capability of the LT8471.

**Avoiding Subharmonic Oscillations:** The LT8471's internal slope compensation circuit will prevent subharmonic oscillations that can occur when the duty cycle is greater than 50%, provided that the inductance exceeds a minimum value. In applications that operate with duty cycles greater than 50%, the inductance must be at least:

$$L_{BOOST} > \frac{V_{CC} \cdot (2 \cdot DC - 1)}{(1 - DC) \cdot f}$$

$$L_{SEPIC} > \frac{V_{CC} \cdot (2 \cdot DC - 1)}{(1 - DC) \cdot f}$$

$$L_{2L_{-}INV} > \frac{V_{CC} \cdot (2 \cdot DC - 1)}{(1 - DC) \cdot f}$$

$$L_{BUCK} > \frac{V_{CC} \cdot (2 \cdot DC - 1)}{f}$$

$$L_{1L_{-}INV} > \frac{V_{CC} \cdot (2 \cdot DC - 1)}{(1 - DC) \cdot f}$$

$$L_{ZETA} > \frac{V_{CC} \cdot (2 \cdot DC - 1)}{(1 - DC) \cdot f}$$

where:

L = L1||L2 for dual uncoupled inductor topologies.

L = L1 = L2 for dual-coupled inductor topologies.

DC = Switch duty cycle in steady state.

$V_{CC}$  = Positive input voltage to the DC/DC converter. See the Typical Applications section for examples.

f = Switching frequency.

**Maximum Inductance:** Excessive inductance can reduce current ripple to levels that are difficult for the current comparator (A3 in the Block Diagram) to easily distinguish, thus causing duty cycle jitter and/or poor regulation. The maximum inductance can be calculated using:

$L_{MAX} = \frac{V_{CC} - V_{CESAT}}{I_{MIN(RIPPLE)} \bullet f} \bullet DC$

for inverting, boost, ZETA and SEPIC topologies, or:

$$L_{MAX} = \frac{(1 - DC) \bullet V_{CC} - V_{CESAT}}{I_{MIN(RIPPLE)} \bullet f} \bullet DC$$

for the buck topology.

where:

$L_{MAX} = L1||L2$  for dual uncoupled inductor topologies.

$L_{MAX} = L1 = L2$  for dual-coupled inductor topologies.

I(MIN)RIPPLE is typically 120mA.

DC = Switch duty cycle in steady state.

$V_{CC}$  = Positive input voltage to the DC/DC converter. See the Typical Applications section for examples.

f = Switching frequency.

**Maximum Current Rating:** Finally, the inductor(s) must be rated to handle the peak operating current to prevent inductor saturation resulting in efficiency loss. In steady state, the peak input inductor current (continuous conduction mode only) is given by:

$$I_{L_PEAK} = \frac{|V_{OUT} \bullet I_{OUT}|}{V_{CC} \bullet \eta} + \frac{(V_{CC} - V_{CESAT}) \bullet DC}{2 \bullet L \bullet f} (BOOST)$$

$$I_{L_{PEAK}} = \frac{|V_{OUT} \bullet I_{OUT}|}{V_{CC} \bullet \eta} + \frac{(V_{CC} - V_{CESAT}) \bullet DC}{2 \bullet L \bullet f} (1L_{INV})$$

$$I_{L_{PEAK}} = I_{OUT} + \frac{(V_{CC} - V_{CESAT}) \bullet DC \bullet (1 - DC)}{2 \bullet L \bullet f} (BUCK)$$

$$I_{L1\_PEAK} = \frac{|V_{OUT} \bullet I_{OUT}|}{V_{CC} \bullet \eta} + \frac{(V_{CC} - V_{CESAT}) \bullet DC}{2 \bullet L1 \bullet f} (SEPIC)$$

$$I_{L2\_PEAK} = I_{OUT} + \frac{(V_{OUT} + V_D) \bullet (1 - DC)}{2 \bullet L2 \bullet f} (SEPIC)$$

$$I_{L1\_PEAK} = \frac{|V_{OUT} \bullet I_{OUT}|}{V_{CC} \bullet \eta} + \frac{(V_{CC} - V_{CESAT}) \bullet DC}{2 \bullet L1 \bullet f} (2L\_INV)$$

$$I_{L2\_PEAK} = I_{OUT} + \frac{(|V_{OUT}| + V_D) \cdot (1 - DC)}{2 \cdot L2 \cdot f} (2L_INV)$$

$$I_{L1\_PEAK} = \frac{|V_{OUT} \bullet I_{OUT}|}{V_{CC} \bullet \eta} + \frac{(V_{CC} - V_{CESAT}) \bullet DC}{2 \bullet L1 \bullet f} (ZETA)$$

$$I_{L2\_PEAK} = I_{OUT} + \frac{(|V_{OUT}| - V_D) \bullet (1 - DC)}{2 \bullet L_2 \bullet f} (ZETA)$$

Note that the inductor current can be higher during load transients. It can also be higher during start-up if inad-equate soft-start capacitance is used.

#### **Capacitor Selection (Primary Channels)**

Low ESR (equivalent series resistance) capacitors should be used at the output to minimize the output ripple voltage. Multilayer ceramic capacitors are an excellent choice. as they have an extremely low ESR and are available in very small packages. X5R or X7R dielectrics are preferred, as these materials retain their capacitance over wider voltage and temperature ranges. A 4.7µF to 20µF output capacitor is sufficient for most applications, but systems with very low output currents may need only a 1µF or 2.2µF output capacitor. Always use a capacitor with a sufficient voltage rating. Many capacitors rated at 2.2µF to 20µF, particularly 0805 or 0603 case sizes, have greatly reduced capacitance at the desired output voltage. Solid tantalum or OS-CON capacitors can be used, but they will occupy more board area than ceramic ones and will have higher ESR with greater output ripple.

Low ESR capacitors should also be used as the input decoupling capacitors, which should be placed as closely as possible to the LT8471. Ceramic capacitors make a good choice for this purpose. A  $2.2\mu$ F to  $4.7\mu$ F input capacitor is sufficient for most applications.

Table 2 shows a list of several ceramic capacitor manufacturers. Consult the manufacturers for detailed information on their entire selection of ceramic capacitors.

| Table 2. Gerannic Gapacitor Man |                 |

|---------------------------------|-----------------|

| VENDOR                          | WEB             |

| Kemet                           | www.kemet.com   |

| Murata                          | www.murata.com  |

| Taiyo-Yuden                     | www.t-yuden.com |

| TDK                             | www.tdk.com     |

#### Table 2. Ceramic Capacitor Manufacturers

#### **Compensation Theory (Primary Channels)**

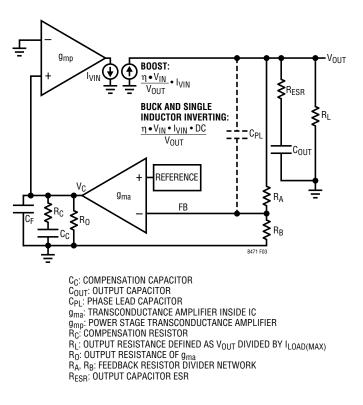

Like all other current mode switching regulators, the primary channels of LT8471 need to be compensated for stable and efficient operation. For each primary channel, two feedback loops are used—a fast current loop which does not require compensation, and a slower voltage loop which does. In order to reduce the PCB footprint, the voltage loop compensation network is integrated inside the LT8471. Therefore, only the inductor and the output capacitor are available for adjusting the loop stability.

Standard bode plot analysis can be used to analyze and adjust the voltage feedback loop.

As with any feedback loop, identifying the gain and phase contribution of the various elements in the loop is critical. Figure 3 shows the key equivalent elements of a boost/ buck/inverting converter. Because of the fast current control loop, the power stage of the IC, inductor and diode have been replaced by a combination of the equivalent transconductance amplifier  $g_{mp}$  and the current controlled current source (which converts  $I_{VIN}$  to  $\eta \cdot V_{IN} \cdot I_{VIN}/V_{OUT}$  for boost converters,  $I_{VIN}$  to  $\eta \cdot V_{IN} \cdot DC/V_{OUT}$  for buck and single inductor inverting converters).  $g_{mp}$  acts as a current source where the peak input current,  $I_{VIN}$ , is proportional to the VC voltage.  $\eta$  is the efficiency of the switching regulator, and is typically about 88%.

Note that the maximum output currents of  $g_{mp}$  and  $g_{ma}$  are finite. The limits for  $g_{mp}$  are in the Electrical Characteristics section (switch current limit), and  $g_{ma}$  is nominally limited to about  $\pm 5\mu$ A.

Figure 3. Boost/Buck/Inverting Converter Equivalent Model

From Figure 3, the DC gain, poles and zeros can be calculated as follows:

DC Gain:

Boost Converters:

$$A_{DC} = (g_{ma} \bullet R_0) \bullet g_{mp} \bullet \left(\eta \bullet \frac{V_{IN}}{V_{OUT}} \bullet \frac{R_L}{2}\right)$$

$$\bullet \frac{R_B}{R_A + R_B}$$

**Buck Converters:**

$$A_{DC} = (g_{ma} \bullet R_0) \bullet g_{mp} \bullet (\eta \bullet R_L) \bullet \frac{R_B}{R_A + R_B}$$

Single Inductor Inverting Converters:

$$\begin{aligned} \mathsf{A}_{\mathsf{DC}} &= (\mathsf{g}_{\mathsf{ma}} \bullet \mathsf{R}_{\mathsf{O}}) \bullet \mathsf{g}_{\mathsf{mp}} \bullet \left( \eta \bullet \frac{\mathsf{V}_{\mathsf{IN}}}{\mathsf{V}_{\mathsf{IN}} + 2 \bullet \left| \mathsf{V}_{\mathsf{OUT}} \right|} \bullet \mathsf{R}_{\mathsf{L}} \right) \\ &\bullet \frac{\mathsf{R}_{\mathsf{B}}}{\mathsf{R}_{\mathsf{A}} + \mathsf{R}_{\mathsf{B}}} \end{aligned}$$

Output Pole:

Boost Converters:

$$P1 = \frac{2}{2 \cdot \pi \cdot R_L \cdot C_{OUT}}$$

Buck Converters:  $P1 = \frac{1}{2 \cdot \pi \cdot R_L \cdot C_{OUT}}$

Single Inductor Inverting Converters:

$$P1 = \frac{2 \bullet \left| V_{OUT} \right| + V_{IN}}{2 \bullet \pi \bullet R_L \bullet C_{OUT} \bullet \left( V_{IN} + \left| V_{OUT} \right| \right)}$$

Error Amp Pole: P2 =

$$\frac{1}{2 \cdot \pi \cdot R_0 \cdot C_C}$$

Error Amp Zero: Z1 =  $\frac{1}{2 \cdot \pi \cdot R_C \cdot C_C}$

ESR Zero: Z2 =  $\frac{1}{2 \cdot \pi \cdot R_{ESR} \cdot C_{OUT}}$

High Frequency Pole: P3> $\frac{f_S}{3}$

Phase Lead Zero: Z4 =  $\frac{1}{2 \cdot \pi \cdot R_A \cdot C_{PL}}$

Phase Lead Pole: P4 =  $\frac{1}{2 \cdot \pi \cdot C_{PL} \cdot \frac{R_A \cdot R_B}{R_A + R_B}}$

Error Amp Filter Pole:

$$P5 = \frac{1}{2 \bullet \pi \bullet \frac{R_C \bullet R_0}{R_C + R_0} \bullet C_F}, C_F < \frac{C_C}{10}$$

RHP Zero:

Boost Converters:

$$Z3 = \frac{(1 - DC)^2 \cdot R_L}{2 \cdot \pi \cdot L}$$

Buck Converters:  $Z3 = \infty$

Single Inductor Inverting Converters:

$$Z3 = \frac{(1 - DC)^2 \cdot R_L}{2 \cdot \pi \cdot DC \cdot L}$$

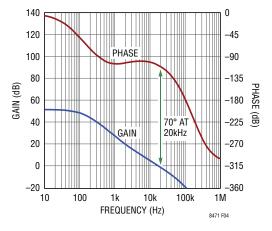

Using the primary channel 1 in Figure 11a as an example, Table 3 shows the parameters used to generate the bode plot shown in Figure 4.

Figure 4. Bode Plot for Example Buck Converter

In Figure 4, the phase is  $-110^{\circ}$  when the gain reaches OdB, giving a phase margin of 70°. The crossover frequency is 20kHz.

| Table 5. Duue Flut Falailleteis |       |       |                      |  |  |  |  |

|---------------------------------|-------|-------|----------------------|--|--|--|--|

| PARAMETER                       | VALUE | UNITS | COMMENT              |  |  |  |  |

| RL                              | 3.3   | Ω     | Application Specific |  |  |  |  |

| C <sub>OUT</sub>                | 94    | μF    | Application Specific |  |  |  |  |

| R <sub>ESR</sub>                | 1     | mΩ    | Application Specific |  |  |  |  |

| R <sub>0</sub>                  | 1.35  | MΩ    | Not Adjustable       |  |  |  |  |

| C <sub>C</sub>                  | 1     | nF    | Not Adjustable       |  |  |  |  |

| C <sub>F</sub>                  | 10    | pF    | Not Adjustable       |  |  |  |  |

| C <sub>PL</sub>                 | 0     | pF    | Optional/Adjustable  |  |  |  |  |

| R <sub>C</sub>                  | 155   | kΩ    | Not Adjustable       |  |  |  |  |

| R <sub>A</sub>                  | 319   | kΩ    | Adjustable           |  |  |  |  |

| R <sub>B</sub>                  | 59    | kΩ    | Adjustable           |  |  |  |  |

| V <sub>OUT</sub>                | 5     | V     | Application Specific |  |  |  |  |

| V <sub>IN</sub>                 | 12    | V     | Application Specific |  |  |  |  |

| g <sub>ma</sub>                 | 70    | µmho  | Not Adjustable       |  |  |  |  |

| g <sub>mp</sub>                 | 7.3   | mho   | Not Adjustable       |  |  |  |  |

| L                               | 10    | μH    | Application Specific |  |  |  |  |

| f <sub>S</sub>                  | 0.45  | MHz   | Adjustable           |  |  |  |  |

#### Table 3. Bode Plot Parameters

The previous discussion is a good start for narrowing down the range of component values so that the overall design meets the stability requirements. To obtain good stability margin and transient response, some fine tuning of the external components, i.e., the inductor and output capacitor may be necessary.

#### **Diode Selection (Primary Channels)**

Schottky diodes, with their low forward-voltage drops and fast switching speeds, are recommended for use with the LT8471. Each of the primary channels need an external diode as the second switch. The diode conducts current only during the switch off-time. The average forward current in normal operation can be calculated from:

$I_{D(AVG)} = I_{OUT} \bullet (1 - DC)$

where  $I_{\text{OUT}}$  is the output load current, and DC is the switch duty cycle in steady state.

Choose a diode rated to handle at least  $I_{D(AVG)}$ . Diodes with higher current rating should be selected to handle increased current during start-up, load transient and/or output short. Choose a Schottky diode with low parasitic capacitance to reduce reverse current spikes through the power switch of the LT8471. In addition, when operating at high ambient temperatures and with high reverse voltages across the Schottky, choose diodes with lower reverse leakage current to avoid excessive heating in the diode. Table 4 lists several Schottky diodes and their manufacturers.

#### Table 4. Diode Vendors

| PARAMETER               | V <sub>R</sub><br>(V) | l <sub>AVE</sub><br>(A) | V <sub>F</sub> AT 1A<br>(mV) | V <sub>F</sub> AT 2A<br>(mV) |

|-------------------------|-----------------------|-------------------------|------------------------------|------------------------------|

| Diodes, Inc.            |                       |                         |                              |                              |

| B120                    | 20                    | 1                       | 500                          |                              |

| B130                    | 30                    | 1                       | 500                          |                              |

| B220                    | 20                    | 2                       |                              | 500                          |

| B230                    | 30                    | 2                       |                              | 500                          |

| DFLS260L                | 60                    | 2                       | 410                          | 620                          |

| Microsemi<br>UPS140     | 40                    | 1                       | 450                          |                              |

| Fairchild<br>SS16       | 60                    | 1                       | 700                          |                              |

| International Rectifier |                       |                         |                              |                              |

| 10BQ030                 | 30                    | 1                       | 420                          | 470                          |

| 20BQ030                 | 30                    | 2                       |                              | 470                          |

#### Skyhook Configuration Requirements

The Skyhook provides the boosted V<sub>IN</sub> voltage required for channels operating in the high side configuration. High side channels have their respective C pin tied to a positive DC voltage supply (usually V<sub>CC</sub>) while the respective E pin toggles. The channel's  $V_{IN}$  pin should be at least 2.2V (typical) higher than the respective C pin to provide adequate base drive for the NPN power switch. Internal circuits monitor the voltage difference between  $V_{IN1}$  and E1 (and  $V_{IN2}$  and E2). If the voltage difference is less than 2.2V (typical), the power switch will be turned off immediately for that clock cycle. Increasing voltage difference between V<sub>IN</sub> and the respective C pin increases power loss and reduces efficiency. V<sub>IN</sub> must not be more than 40V higher than the respective C pin for high side configurations. If use of Skyhook channel is not desired, then the boosted V<sub>IN</sub> voltage can instead be provided by an external power supply or by the output of the opposite channel if the voltage is high enough.

The Skyhook output (SHOUT) is regulated to ~4.25V above the C2 pin voltage and can be connected to the appropriate  $V_{IN}$  pin(s) as shown in the Typical Applications section. When in use, the Skyhook can only be configured as a boost converter (i.e., as in Figure 1a). Also, since SHOUT is regulated to ~4.25V above C2, the C2 pin must be connected to a DC voltage (usually V<sub>CC</sub>) and must not be toggling. Because of this requirement, if channel 2 is used while the Skyhook is operating, channel 2 must be in the high side configuration such as buck or single-inductor inverting. If not being used, the Skyhook channel can be disabled by connecting the C3 pin to ground. When the Skyhook channel is disabled V<sub>IN1</sub> current is reduced.

#### **Capacitor and Diode Selection (Skyhook)**

A low ESR capacitor should be used at the Skyhook output to minimize voltage ripple. Ceramic capacitors make a good choice for this (see the discussion in the Capacitor Selection (Primary Channels) section). The capacitor value can affect stability. Read the upcoming Compensation (Skyhook) section for more information. For the best noise performance, the Skyhook output capacitor should be connected from SHOUT to GND, and the capacitors should be placed close to the pins ( $V_{IN1}$  or  $V_{IN2}$ ) that SHOUT is shorted to. The Skyhook output capacitor can also be connected from SHOUT to the C2 pin (usually  $V_{CC}$ ), as shown in Figure 9a. By doing this, the output voltage of the Skyhook, or the boosted base drive voltage for the primary channels will have better tracking with the supply voltage of the channel. In addition, the voltage across the capacitor is lower, thus reducing the size and required voltage rating of the capacitor.

The Skyhook has a Schottky diode built on-chip. Nevertheless, an external Schottky diode can be connected from C3 to SHOUT to improve performance when load currents are high. The diode choice can be made based on the discussion in the Diode Selection (Primary Channels) section. The output current ( $I_{OUT}$ ) for the Skyhook channel can be estimated as:

$$\mathsf{I}_{\mathsf{OUT}} \cong \frac{(\mathsf{V}_{\mathsf{CC}} + 4.25\mathsf{V}) \bullet (\mathsf{I}_{\mathsf{OUT1}} \bullet \mathsf{DC}_1 + \mathsf{I}_{\mathsf{OUT2}} \bullet \mathsf{DC}_2)}{\beta \bullet \mathsf{V}_{\mathsf{CC}} \bullet \eta}$$

where:

V<sub>CC</sub> = Input voltage of the Skyhook.

$I_{OUT1}$  = Average output current of channel 1 if  $V_{IN1}$  is connected to SHOUT (0 otherwise).

$I_{OUT2}$  = Average output current of channel 1 if  $V_{IN2}$  is connected to SHOUT (0 otherwise).

DC1 = Duty cycle of channel 1 in steady state.

DC2 = Duty cycle of channel 2 in steady state.

$\eta$  = Power conversion efficiency of the Skyhook (typically 87%).

$\beta$  = Channel 1/channel 2 power switch beta (typically 35)

#### Inductor Selection (Skyhook)

The general guidelines are the same as the ones for primary channels, and can be found in the previous section.

**Minimum Inductance:** There are three conditions that limit the minimum inductance for the Skyhook boost converter:

- 1. Provide adequate load current;

- 2. Avoid excessive power switch current overshoot;

- 3. Maintain good loop stability (see the subsequent Compensation (Skyhook) section).

Choose an inductance that satisfies the minimum requirements for all three criteria. At least 20% of additional margin is recommended for the inductance.

**Adequate Load Current:** Starting by assuming the Skyhook operates in discontinuous mode (DCM), the minimum inductance ( $L_{DCM(MIN)}$ ) to provide adequate load current is:

$$L_{\text{DCM}(\text{MIN})} > \frac{(I_{\text{OUT1}} \bullet \text{DC1} + I_{\text{OUT2}} \bullet \text{DC2}) \bullet 4.25 \text{V} \bullet 2}{35 \bullet \eta \bullet f \bullet I_{\text{LIM}}^2}$$

Next, verify if the Skyhook will actually operate in DCM with the following inequality:

$$I_{\text{LIM}} \bullet L_{\text{DCM}(\text{MIN})} \bullet f \bullet \left(\frac{1}{V_{\text{CC}}} + \frac{1}{4.25V}\right) < 1$$

If this inequality is true, then the Skyhook will operate in DCM, and  $I_{DCM(MIN)}$  is the minimum inductance needed to provide adequate load current. Otherwise, the Skyhook will operate in continuous mode (CCM) when providing maximum load current, and the minimum inductance  $(L_{CCM(MIN)})$  needed is:

$L_{CCM(MIN)} >$

$\frac{\mathsf{DC}_{\mathsf{SH}} \bullet \mathsf{V}_{\mathsf{CC}}}{2 \bullet \mathsf{f} \bullet \left(\mathsf{I}_{\mathsf{LIM}} - \frac{(\mathsf{V}_{\mathsf{CC}} + 4.25\mathsf{V}) \bullet (\mathsf{I}_{\mathsf{OUT1}} \bullet \mathsf{DC1} + \mathsf{I}_{\mathsf{OUT2}} \bullet \mathsf{DC2})}{35 \bullet \mathsf{V}_{\mathsf{CC}} \bullet \eta}\right)}$

where:

DC<sub>SH</sub> = Skyhook duty cycle in steady state:

$$\mathsf{DC}_{\mathsf{SH}} \cong \frac{4.25\mathsf{V} + \mathsf{V}_{\mathsf{DSH}}}{\mathsf{V}_{\mathsf{C2}} + 4.25\mathsf{V} + \mathsf{V}_{\mathsf{DSH}}}$$

$V_{\text{DSH}}$  = Skyhook diode forward voltage drop (see the Electrical Characteristics section).

V<sub>CC</sub>= Input voltage of the Skyhook.

I<sub>LIM</sub> = Skyhook switch fault current limit, typically 500mA.

$I_{OUT1}$  = Average output current of channel 1 if  $V_{IN1}$  is connected to SHOUT (0 otherwise).

$I_{OUT2}$  = Average output current of channel 2 if  $V_{IN2}$  is connected to SHOUT (0 otherwise).

DC1 = Duty cycle of channel 1 in steady state.

DC2 = Duty cycle of channel 2 in steady state.

$\eta$  = Power conversion efficiency of Skyhook (typically 87%).

f = Switching frequency.

Skyhook Power Switch Current Overshoot: In order to avoid excessive current overshoot in the Skyhook power switch,  $L_{OS(MIN)}$  should be:

$$L_{OS(MIN)} > \frac{V_{CC} \bullet t_D}{I_{OS}}$$

where:

V<sub>CC</sub> = Input voltage of the Skyhook.

$t_D$  = Skyhook fault current limit comparator delay (typically 50ns).

$I_{OS}$  = The amount of overshoot current that can be tolerated (typically 100mA).

**Current Rating:** The maximum switch current limit for the Skyhook is 500mA. Choose an inductor that has a saturation current of 500mA or higher to avoid saturating the inductor.

#### Compensation (Skyhook)

Like the primary channels, the Skyhook is internally compensated, and the loop stability is adjusted through the inductor and the output capacitor. In most applications, a 15 $\mu$ H Skyhook inductor such as Würth 744025150. and a 0.47 $\mu$ F Skyhook output capacitor (C3 in the Block Diagram) will give good stability. For high input voltage applications, more inductance is typically required to reduce the current overshoot.

A good technique to compensate the Skyhook regulator is to start with a  $15\mu$ H Skyhook inductor and a  $0.47\mu$ F output capacitor (C3 in the Block Diagram), and use the subsequent list to make additional adjustments if needed.

More output capacitance (C3 in the Block Diagram) can help with:

• Reducing the SHOUT overshoot and undershoot during primary channel(s) load steps.

Less output capacitance (C3 in the Block Diagram) can help with:

- Improving loop stability.

- Reducing peak inductor current during start-up.

More Skyhook inductance can help with:

• Reducing peak inductor current.

Less Skyhook inductance can help with:

• Improving loop stability when the SHOUT current load is consistently high (i.e., the primary channel(s) powered by SHOUT is switching every cycle).

Adding a resistor between SHOUT and C2, to introduce a few mA of constant load, can help with:

• Improving the loop stability, SHOUT undershoot and overshoot when the SHOUT current load is consistently very light (i.e., the primary channel(s) powered by SHOUT is not switching every cycle).

#### **Thermal Considerations**

For the LT8471 to deliver its full output power, it is imperative that a good thermal path be provided to dissipate the heat generated within the package. This can be accomplished by taking advantage of the thermal pad on the underside of the IC. It is recommended that multiple vias in the printed circuit board be used to conduct heat away from the IC and into a copper plane with as much area as possible.

| DEFINITION OF VARIABLES                                                                                           | EQUATIONS                                                                                            | DESIGN EXAMPLE                                            | VALUE                     |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------|

| DC = Switch Duty Cycle                                                                                            | $DC = \frac{V_{OUT} - V_{IN} + V_D}{V_{OUT} + V_D - V_{CESAT}}$                                      | $DC = \frac{12V - 5V + 0.45V}{12V + 0.45V - 0.21V}$       | DC = 60.9%                |

| $I_{IN}$ = Average Switch Current<br>$\eta$ = Power Conversion Efficiency<br>(typically 88% at high currents)     | $I_{IN} = \frac{V_{OUT} \bullet I_{OUT}}{\eta \bullet V_{IN}}$                                       | $I_{\rm IN} = \frac{12V \bullet 0.67A}{0.88 \bullet 5V}$  | I <sub>IN</sub> = 1.85A   |

| P <sub>SWDC</sub> = Switch I <sup>2</sup> R Loss (DC)<br>R <sub>SW</sub> = Switch Resistance<br>(typically 200mΩ) | $P_{SWDC} = DC \bullet I_{IN}^2 \bullet R_{SW}$                                                      | P <sub>SWDC</sub> = 0.609 • (1.85A) <sup>2</sup> • 200mΩ  | P <sub>SWDC</sub> = 417mW |

| P <sub>SWAC</sub> = Switch Dynamic<br>Loss (AC)                                                                   | $P_{SWAC} = 13ns \bullet I_{IN} \bullet V_{OUT} \bullet f_{OSC}$                                     | P <sub>SWAC</sub> = (13ns) • 1.85A • 12V • (1MHz)         | P <sub>SWAC</sub> = 289mW |

| P <sub>BDC</sub> = Base Drive Loss (DC)                                                                           | $P_{BDC} = \frac{V_{IN} \bullet I_{IN} \bullet DC}{38}$                                              | $P_{BDC} = \frac{5V \cdot 1.85A \cdot 0.609}{38}$         | P <sub>BDC</sub> = 148mW  |

| P <sub>INP</sub> = Input Power Loss                                                                               | $P_{INP} = 2.5 \text{mA} \bullet V_{IN}$                                                             | P <sub>INP</sub> = 2.5mA • 5V                             | P <sub>INP</sub> = 12.5mW |

|                                                                                                                   | $P_{\text{TOTAL}} = (P_{\text{SWDC}} + P_{\text{SWAC}} + P_{\text{BDC}}) \bullet 2 + P_{\text{INP}}$ | P <sub>TOTAL</sub> = (0.417 + 0.289 + 0.148) • 2 + 0.0125 | $P_{TOTAL} = 1.72W$       |

#### Table 5. LT8471 Power Dissipation

#### **Power and Thermal Calculations**

Power dissipation in the LT8471 chip comes from four primary sources: switch I<sup>2</sup>R losses, switch dynamic losses, NPN base drive DC losses, and miscellaneous input current losses. These formulas assume continuous mode operation, so they should not be used for calculating thermal losses or efficiency in discontinuous mode or at light load currents.

The following example calculates the power dissipation in the LT8471 for a particular boost application on both CH1 and CH2 ( $V_{IN} = 5V$ ,  $V_{OUT} = 12V$ ,  $I_{OUT} = 0.67A$ ,  $f_{OSC} = 1MHz$ ,  $V_D = 0.45V$ ,  $V_{CESAT} = 0.21V$ ).

To calculate die junction temperature, use the appropriate thermal resistance number and add in worst-case ambient temperature:

$T_J = T_A + \theta_{JA} \bullet P_{TOTAL}$

where  $T_J = Die Junction Temperature$ ,  $T_A = Ambient Temperature$ ,  $P_{TOTAL}$  is the final result from the calculations shown in Table 5, and  $\theta_{JA}$  is the thermal resistance from the silicon junction to the ambient air.

The  $\theta_{JA}$  value is 38°C/W for the 20-lead TSSOP package and 44°C/W for the 28-lead (4mm × 5mm) QFN package. In practice, lower  $\theta_{JA}$  values can be realized if board layout is performed with appropriate grounding (accounting for heat sinking properties of the board) and other considerations listed in the Layout Guidelines section.

#### Thermal Lockout

A fault condition occurs when the die temperature exceeds 164°C (see Operation Section), and the part goes into thermal lockout. The fault condition ceases when the die temperature drops by ~1.5°C (nominal).

#### V<sub>IN</sub> Ramp Rate

While initially powering a switching converter application, the V<sub>IN</sub> ramp rate should be limited. High V<sub>IN</sub> ramp rates can cause excessive inrush currents in the passive components of the converter. This can lead to current and/or voltage

overstress and may damage the passive components or the chip. Ramp rates less than 500mV/µs, depending on component parameters, will generally prevent these issues. Also, be careful to avoid hot-plugging. Hot-plugging occurs when an active voltage supply is "instantly" connected or switched to the input of the converter. Hot-plugging results in very fast input ramp rates and is not recommended. Finally, for more information, refer to Linear application note AN88, which discusses voltage overstress that can occur when an inductive source impedance is hot-plugged to an input pin bypassed by ceramic capacitors.

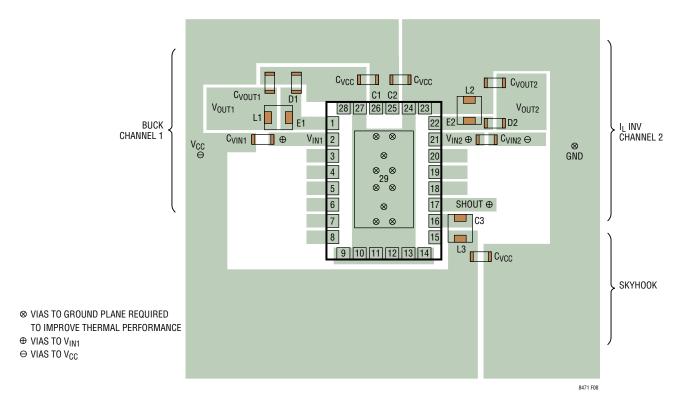

#### Layout Guidelines

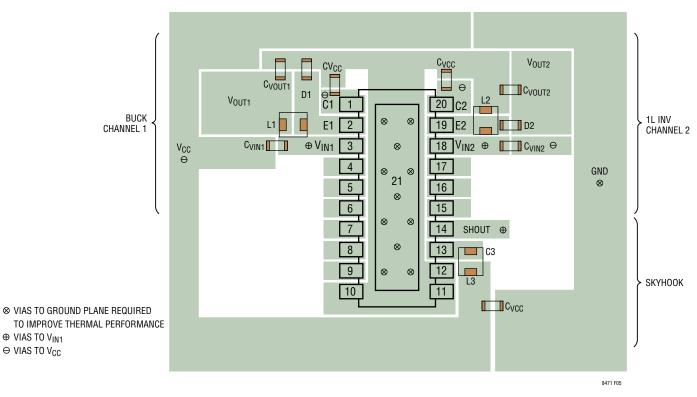

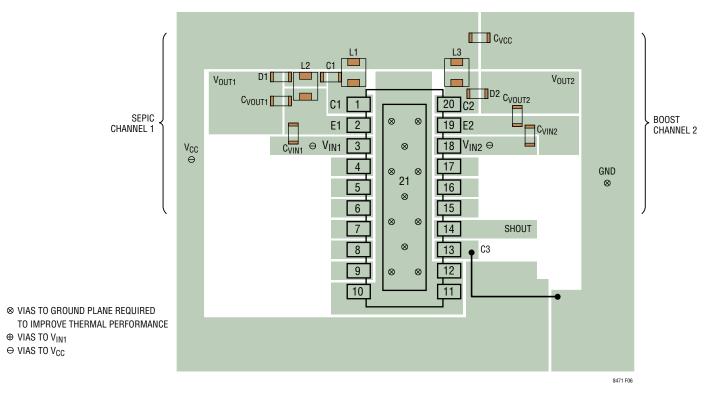

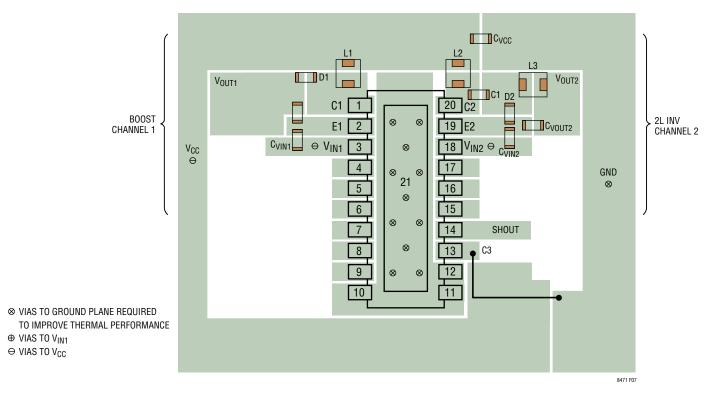

As with all high frequency switchers, when considering layout, care must be taken to achieve optimal electrical, thermal and noise performance. One will not get advertised performance with a careless layout. To prevent noise, both radiated and conducted, the high speed switching current paths must be kept as short as possible. For each channel, the high speed switching current flows in a loop through the following components:

- **Boost:** NPN power switch (C-E pins), external Schottky diode and output capacitor

- **Buck:** NPN power switch (C-E pins), external Schottky diode and input capacitor

- **1L Inverting:** NPN power switch (C-E pins), external Schottky diode, input capacitor and output capacitor

The area inside the loop formed by these components should be kept as small as possible. This is implemented in the suggested layouts shown in Figure 5, Figure 6 and Figure 7. Shortening the loop will also reduce the parasitic trace inductance. As the NPN switch turns off, the parasitic inductance can produce a flyback spike across the LT8471 switch. When operating at higher currents and output voltages, with poor layout, the spike can generate voltages across the switch that may exceed its absolute maximum rating. A ground plane should also be used under the switcher circuitry to prevent interplane coupling and overall noise. However, there should be no ground plane under the planes that are connected to

the switching pins to keep the stray capacitance on the switching pins small.