# ADP1034ACPZ-1-R7

# 3-Channel Isolated Micropower Management Unit with Seven Digital Isolators and Programmable Power Control

## **FEATURES**

- ▶ Wide input supply voltage range: 4.5 V to 60 V

- ▶ Integrated flyback power switch

- Generates isolated, independent, resistor-programmable bipolar outputs and factory-programmable buck output

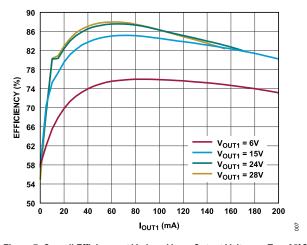

- V<sub>OUT1</sub>: 6 V to 28 V

- V<sub>OUT2</sub>: 5.0 V

- ▶ V<sub>OUT3</sub>: -24 V to -2 V

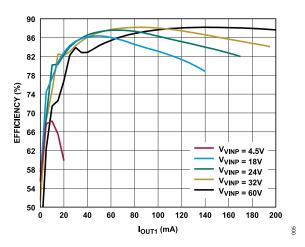

- ▶ 86% typical efficiency at 2.61 W output power

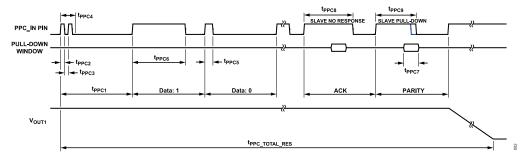

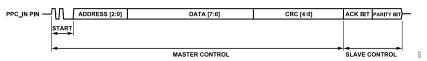

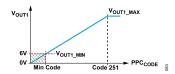

- Programmable power control pin (PPC\_IN) for adjusting V<sub>OUT1</sub> through serial command

- ▶ Uses a 1:1 ratio transformer for simplified transformer design

- ▶ Adjustable switching frequency via SYNC input

- ▶ Peak current limiting and overvoltage protection

- ▶ Internal compensation and soft start control per regulator

- ▶ Precision enable input

- ▶ High speed, low propagation delay, SPI signal isolation channels

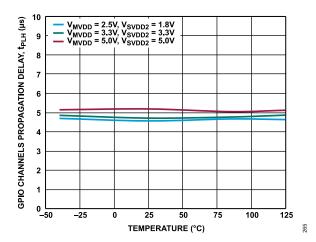

- ▶ Three 100 kbps general-purpose isolated data channels

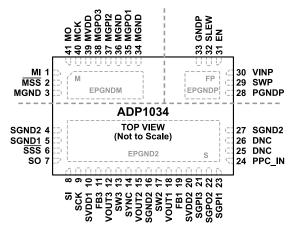

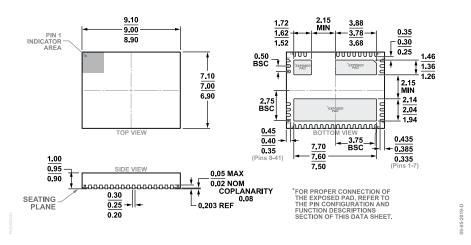

- ▶ 41-lead, 9 mm × 7 mm LFCSP form factor enables small overall solution size

- ► -40°C to +125°C operating junction temperature range

- Safety and regulatory approvals (pending)

- ▶ CISPR11 Class B radiated emission

- ▶ UL recognition: 2500 V rms for 1 minute per UL 1577

- CSA Component Acceptance Notice 5A

- 300 V rms basic insulation between slave, master, and field power domains (IEC 61010-1, pending)

- VDE certificate of conformity

- ▶ DIN V VDE 0884-10 (VDE 0884-10):2006-12

- ► V<sub>IORM</sub> = 565 V peak

#### **APPLICATIONS**

- Industrial automation and process control

- Instrumentation and data acquisition systems

- ▶ Data and power isolation

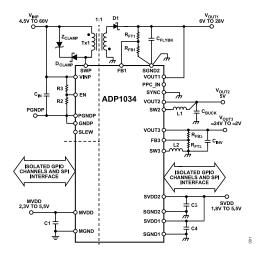

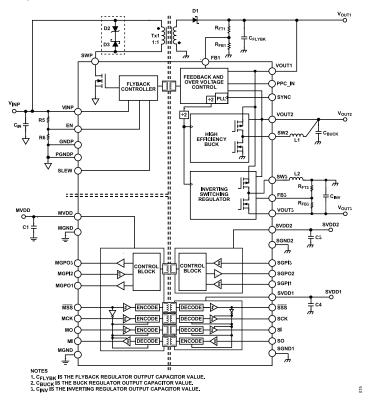

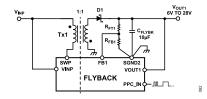

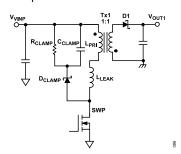

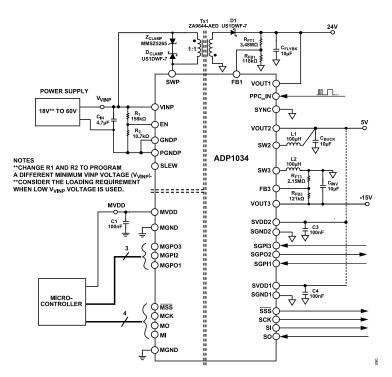

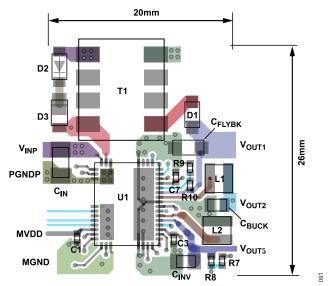

## TYPICAL APPLICATION CIRCUIT

Figure 1.

## **GENERAL DESCRIPTION**

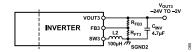

The ADP1034 is high performance, isolated micropower management unit (PMU) that combines an isolated flyback dc-to-dc regulator, an inverting buck boost dc-to-dc regulator, and a buck dc-to-dc regulator, providing three isolated power rails. The ADP1034 includes four high speed serial peripheral interface (SPI) isolation channels and three general-purpose isolators for channel to channel applications where low power dissipation and small solution size are required.

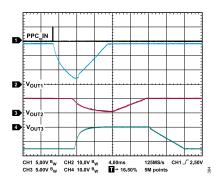

Operating over an input voltage range of 4.5 V to 60 V, the ADP1034 generates isolated output voltage ranges of 6 V to 28 V for  $V_{OUT1}$ , -24 V to -2 V for  $V_{OUT3}$ , and a factory-programmable voltage of 5 V for  $V_{OUT2}$ . Additionally, a PPC\_IN pin is provided for adjusting the  $V_{OUT1}$  setting on demand through a serial command that allows higher efficiency in system level applications.

By default, the ADP1034 flyback regulator operates at a 250 kHz switching frequency, and the buck and inverting regulators operate at 125 kHz. The ADP1034 can be driven by an external oscillator in the range of 350 kHz to 750 kHz to ease noise filtering in sensitive applications.

The digital isolators integrated in the ADP1034 use Analog Devices, Inc., iCoupler® chip scale transformer technology optimized for low power and low radiated emissions. The ADP1034 is available in a 9 mm × 7 mm, 41-lead lead frame chip scale package (LFCSP) and is rated for a −40°C to +125°C operating junction temperature range.

Analog Devices is in the process of updating documentation to provide terminology and language that is culturally appropriate. This is a process with a wide scope and will be phased in as quickly as possible. Thank you for your patience.

# **TABLE OF CONTENTS**

| Features1                                      | Flyback Regulator                       | 26 |

|------------------------------------------------|-----------------------------------------|----|

| Applications1                                  | Buck Regulator                          |    |

| Typical Application Circuit1                   | Inverting Regulator                     | 28 |

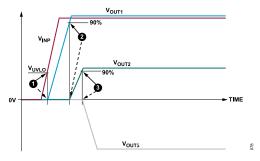

| General Description1                           | Power-Up Sequence                       | 29 |

| Specifications3                                | Oscillator and Synchronization          | 29 |

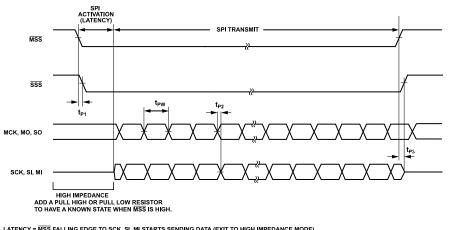

| Timing Characteristics7                        | Thermal Shutdown                        | 29 |

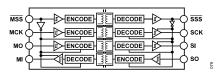

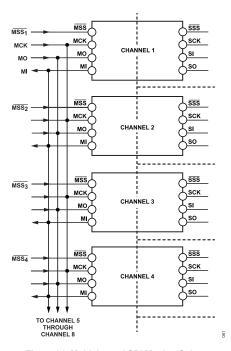

| Regulatory Information8                        | Data Isolation                          | 29 |

| Electromagnetic Compatibility8                 | Applications Information                | 32 |

| Insulation and Safety Related Specifications 8 | Component Selection                     | 32 |

| DIN V VDE 0884-10 (VDE V 0884-10)              | Flyback Regulator Components Selection  | 33 |

| Insulation Characteristics9                    | Buck Regulator Component Selection      | 37 |

| Absolute Maximum Ratings10                     | Inverting Regulator Component Selection | 37 |

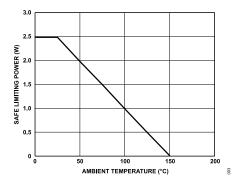

| Thermal Resistance10                           | Insulation Lifetime                     | 38 |

| Electrostatic Discharge (ESD) Ratings10        | Thermal Analysis                        | 38 |

| ESD Caution10                                  | Detailed Typical Application Circuit    | 38 |

| Maximum Continuous Working Voltage 10          | PCB Layout Considerations               | 40 |

| Pin Configuration and Function Descriptions11  | Outline Dimensions                      | 41 |

| Typical Performance Characteristics13          | Ordering Guide                          | 41 |

| Theory of Operation25                          | Evaluation Boards                       | 41 |

|                                                |                                         |    |

# **REVISION HISTORY**

5/2022—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 41

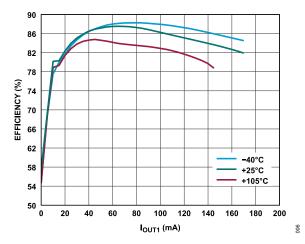

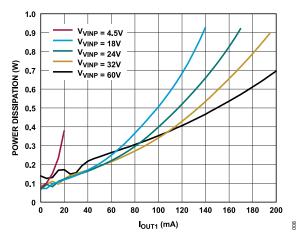

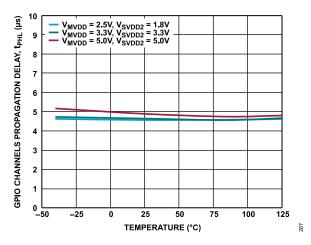

VINP voltage ( $V_{VINP}$ ) = 24 V, MVDD voltage ( $V_{MVDD}$ ) = 3.3 V, SVDDx voltage ( $V_{SVDDx}$ ) = 3.3 V, VOUT1 voltage ( $V_{OUT1}$ ) = 24 V, VOUT2 voltage ( $V_{OUT2}$ ) = 5 V, VOUT3 voltage ( $V_{OUT3}$ ) = -15 V, and  $T_A$  = 25°C for typical specifications. Minimum and maximum specification apply over the entire operating range of 4.5 V  $\leq$  V<sub>VINP</sub>  $\leq$  60 V, 2.3 V  $\leq$  V<sub>MVDD</sub>  $\leq$  5.5 V, 1.8 V  $\leq$  V<sub>SVDDx</sub>  $\leq$  5.5 V, and -40°C  $\leq$   $T_J$   $\leq$  +125°C, unless otherwise noted.

Table 1.

| Parameter                   | Symbol                                    | Min  | Тур          | Max      | Unit   | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------|-------------------------------------------|------|--------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Supply voltage Range  |                                           |      |              |          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VINP                        | V <sub>VINP</sub>                         | 4.5  |              | 60       | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MVDD                        | V <sub>MVDD</sub>                         | 2.3  |              | 5.5      | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SVDD                        | $V_{SVDDx}$                               | 1.8  |              | 5.5      | V      | Applies to SVDD1 and SVDD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

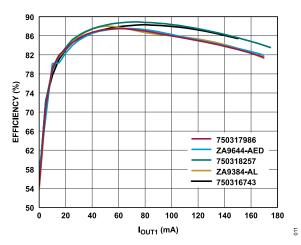

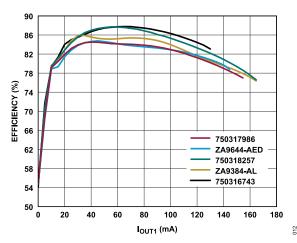

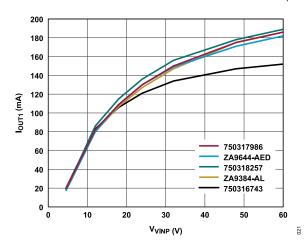

| OUTPUT POWER AND EFFICIENCY |                                           |      |              |          |        | Transformer = ZA9644-AED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Total Output Power          |                                           |      | 690          |          | mW     | $V_{OUT1}$ current ( $I_{OUT1}$ ) = 25 mA, $V_{OUT2}$ current ( $I_{OUT2}$ ) = 6 mA, $V_{OUT3}$ current ( $I_{OUT3}$ ) = -4 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                             |                                           |      | 2610         |          | mW     | $I_{OUT1}$ = 105 mA, $I_{OUT2}$ = 6 mA, $I_{OUT3}$ = -4 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Efficiency                  |                                           |      | 83.9         |          | %      | $I_{OUT1}$ = 25 mA, $I_{OUT2}$ = 6 mA, $I_{OUT3}$ = -4 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                             |                                           |      | 86           |          | %      | $I_{OUT1}$ = 105 mA, $I_{OUT2}$ = 6 mA, $I_{OUT3}$ = -4 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

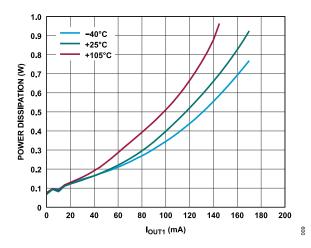

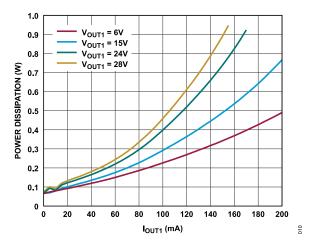

| Power Dissipation           |                                           |      | 132          |          | mW     | $I_{OUT1}$ = 25 mA, $I_{OUT2}$ = 6 mA, $I_{OUT3}$ = -4 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                             |                                           |      | 427          |          | mW     | I <sub>OUT1</sub> = 105 mA, I <sub>OUT2</sub> = 6 mA, I <sub>OUT3</sub> = -4 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| QUIESCENT CURRENT           |                                           |      |              |          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VINP                        |                                           |      |              |          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operating Current           | I <sub>Q_VINP</sub>                       |      | 1.9          |          | mA     | Normal operation, V <sub>OUT1</sub> , V <sub>OUT2</sub> , V <sub>OUT3</sub> = no load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Shutdown Current            | I <sub>SHDN_VINP</sub>                    |      | 125          | 175      | μA     | EN voltage (V <sub>EN</sub> ) = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MVDD                        |                                           |      |              |          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SPI Active Mode             | I <sub>Q_MVDD</sub> (SPI_ACTIVE)          |      | 4.1          | 6.5      | mA     | $V_{lx}^{1}$ = logic low, $\overline{MSS}$ = logic low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                             |                                           |      | 9.2          | 14       | mA     | $V_{lx}^{1}$ = logic high, $\overline{MSS}$ = logic low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

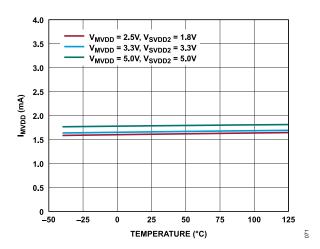

| SPI Low Power Mode          | I <sub>Q_MVDD</sub> (SPI_LOWPWR)          |      | 1.6          | 2.5      | mA     | $V_{lx}^{1}$ = logic low, $\overline{MSS}$ = logic high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0.75                        |                                           |      | 1.6          | 2.5      | mA     | $V_{lx}^{1}$ = logic high, $\overline{MSS}$ = logic high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SVDD1                       |                                           |      | 4.0          | 0.7      |        | V 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SPI Active Mode             | IQ_SVDD1 (SPI_ACTIVE)                     |      | 1.8          | 2.7      | mA     | $V_{ x}^{1}$ = logic low, $\overline{SSS}$ = logic low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ODLL D. M.                  |                                           |      | 5.7          | 8.6      | mA     | $V_{IX}^{1}$ = logic high, $\overline{SSS}$ = logic low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SPI Low Power Mode          | I <sub>Q_SVDD1</sub> (SPI_LOWPWR)         |      | 1.8          | 2.7      | mA     | $V_{ x}^{1}$ = logic low, $\overline{SSS}$ = logic high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CVDDO                       |                                           |      | 1.8          | 2.7      | mA<br> | $V_{1x}^{1}$ = logic high, $\overline{SSS}$ = logic high $V_{1x}^{1}$ = logic low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

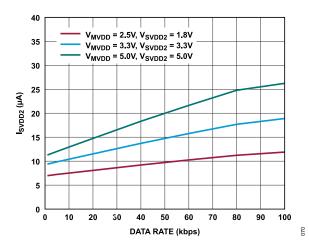

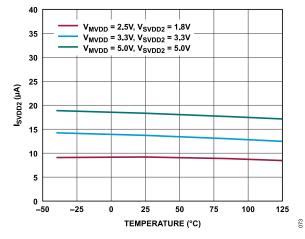

| SVDD2                       | I <sub>Q_SVDD2</sub>                      |      | 15.5<br>15.5 | 22<br>22 | μA     | $V_{lx}^{-1}$ = logic low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UVLO                        |                                           |      | 10.0         |          | μA     | V <sub>IX</sub> . – logic fligit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VINP                        |                                           |      |              |          |        | Relative to PGNDP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Rising Threshold            | V                                         |      | 4.44         | 4.49     | V      | INCIDITION OF THE PROPERTY OF |

| Falling Threshold           | Vuvlo_flyback (Rise) Vuvlo_flyback (fall) | 4.29 | 4.34         | 7.70     | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Hysteresis                  | * UVLO_FLYBACK (FALL)                     | 1.20 | 100          |          | mV     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

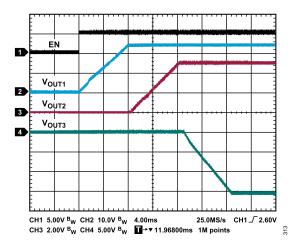

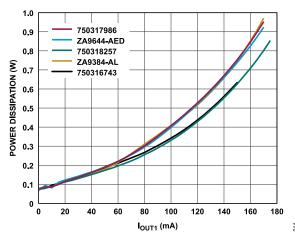

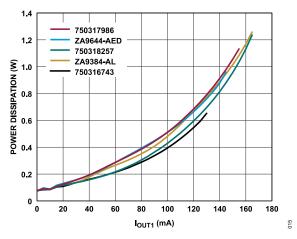

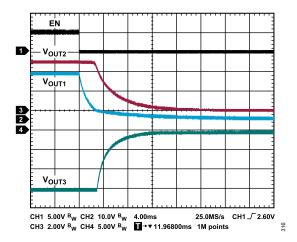

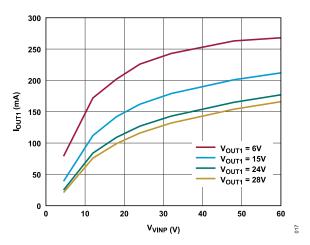

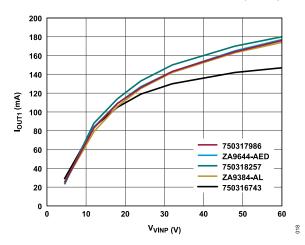

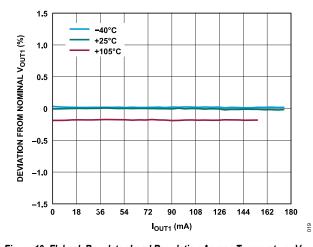

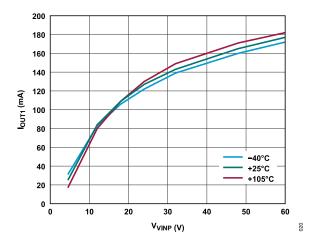

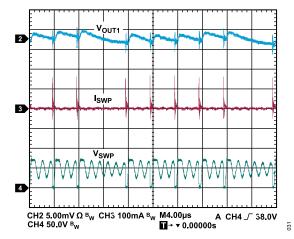

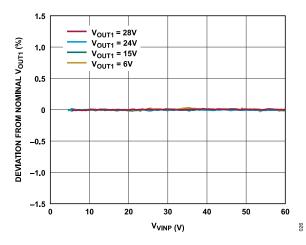

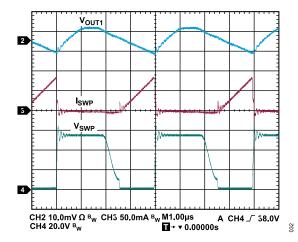

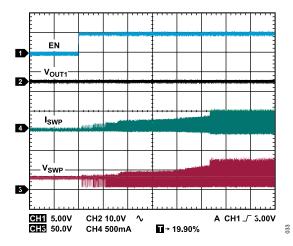

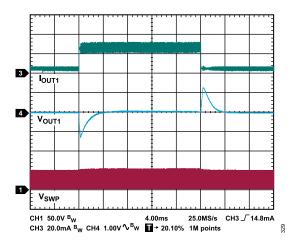

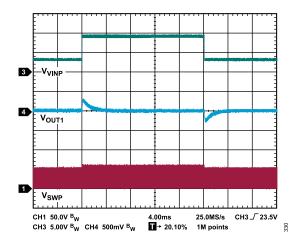

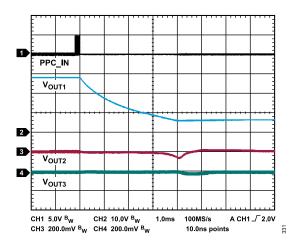

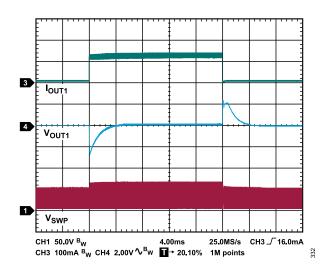

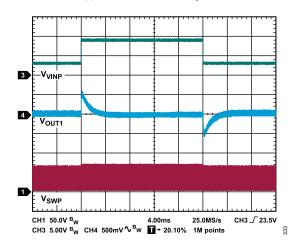

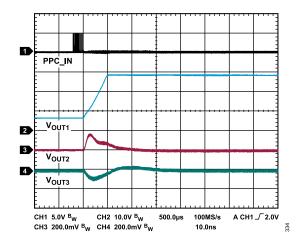

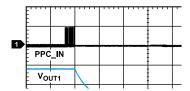

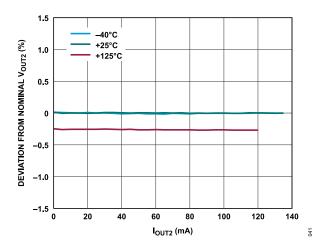

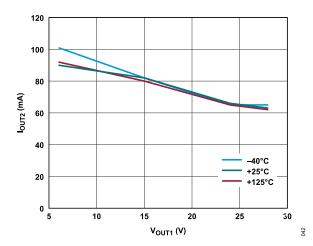

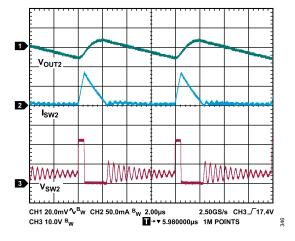

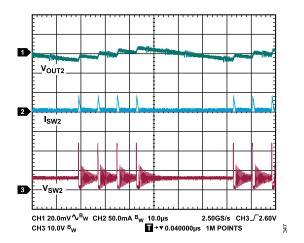

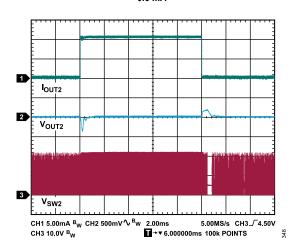

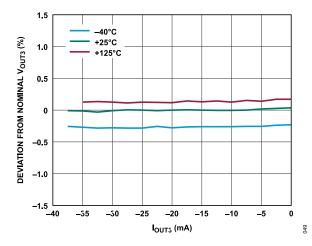

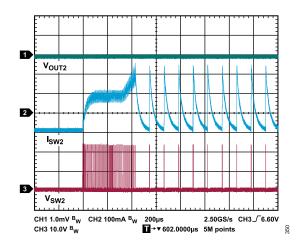

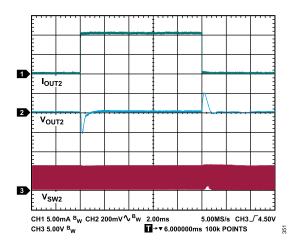

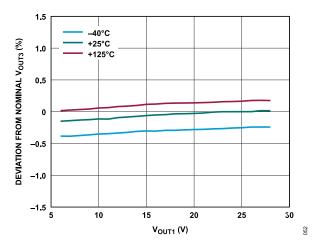

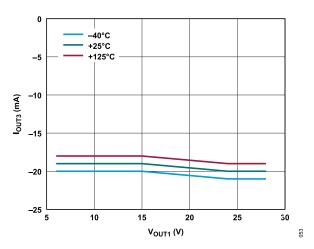

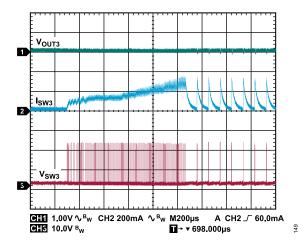

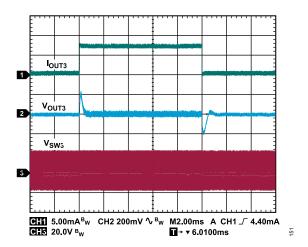

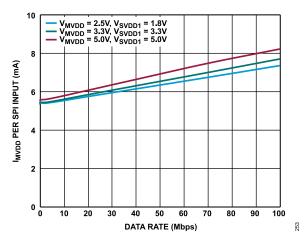

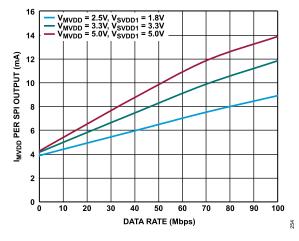

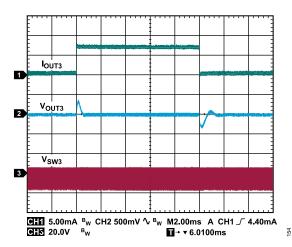

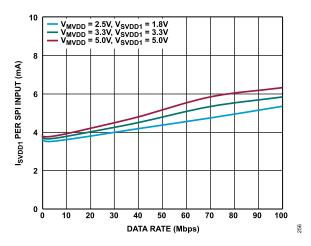

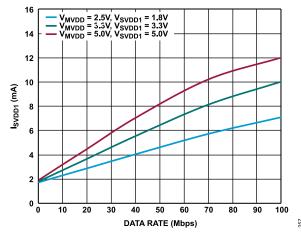

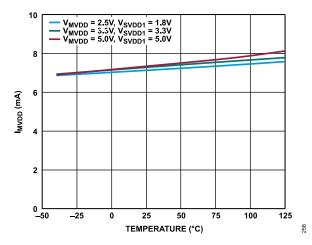

| MVDD                        |                                           |      | 100          |          | •      | Relative to MGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |